雪崩光电二极管(APD)偏置电源及其电流监测

下面列出了参考设计的主要规格、详细的原理图(图1)以及材料清单(表1)。

设计规格与配置

- 2.7V至11V较宽的输入电压范围

- 70V输出电压

- 4mA输出电流

- 400kHz固定开关频率

- -40°C至+125°C工作温度范围

- 微型、8mm x 12mm电路板尺寸

参考设计原理图

图1所示为参考设计的原理图,输入电压范围为2.7V至5.5V。将CP引脚连接到VIN、去掉电荷泵电容(C3),该电路可接受5.5V至11V输入范围。

图1. MAX15031升压转换器原理图,FSW = 400kHz (固定)。

详情介绍

下面列出了参考设计的主要规格、详细的原理图(图1)以及材料清单(表1)。

设计规格与配置

- 2.7V至11V较宽的输入电压范围

- 70V输出电压

- 4mA输出电流

- 400kHz固定开关频率

- -40°C至+125°C工作温度范围

- 微型、8mm x 12mm电路板尺寸

参考设计原理图

图1所示为参考设计的原理图,输入电压范围为2.7V至5.5V。将CP引脚连接到VIN、去掉电荷泵电容(C3),该电路可接受5.5V至11V输入范围。

图1. MAX15031升压转换器原理图,FSW = 400kHz (固定)。

表1. 材料清单(BOM)

| Designator | Value | Description | Part | Footprint | Manufacturer | Quantity |

|---|---|---|---|---|---|---|

| C1 | 1µF, 10V | Capacitor | GRM155R61A105KE15 | 0402 | Murata | 1 |

| C2, C4 | 0.1µF, 16V | Capacitors | GRM155R71C104KA88 | 0402 | Murata | 2 |

| C3, C6 | 0.01µF, 25V | Capacitors | GRM155R71E103KA01D | 0402 | Murata | 2 |

| C5, C8 | 0.1µF, 100V | Capacitors | GCM21BR72A104KA37L | 0805 | Murata | 2 |

| C7 | 0 | Capacitor | Open | 0402 | Open | 1 |

| D1 | 100V, 150mA | Schottky diode | BAT46W-7-F | SOD-123 | Diodes Inc. | 1 |

| L1 | 4.7µH | Inductor | ME3220-472MLB | 3mm x 3mm | Coilcraft | 1 |

| R1 | 348kΩ | Resistor | SMD, 1%, 0.125W | 0402 | Vishay | 1 |

| R2 | 6.34kΩ | Resistor | SMD, 1%, 0.125W | 0402 | Vishay | 1 |

| R3, R6 | 10kΩ | Resistors | SMD, 1%, 0.125W | 0402 | Vishay | 2 |

| R4 | 100Ω | Resistor | SMD, 1%, 0.125W | 0402 | Vishay | 1 |

| R5 | 3.16kΩ | Resistor | SMD, 1%, 0.125W | 0402 | Vishay | 1 |

| U1 | MAX15031 | Boost converter | MAX15031ATE+ | 16-TQFN-EP | Maxim | 1 |

表示本设计性能的波形图

图2和图3给出了图1所示电路的工作性能,从LX节点的电压波形可以看出,转换器工作在非连续模式。输入(VIN)保持为3.3V,电路设计为产生70V输出电压(VOUT)。

图2. 3.3V输入时的VIN (通道1)、VOUT (通道2)和APD (通道3)。

图3. VIN = 3.3V、APD电流为4mA时的LX节点电压(通道1)、VOUT (通道2)和APD输出(通道3)。

图4. VIN = 3.3V、APD电流为4mA时的输入纹波(通道1)和输出纹波(通道2)。

图4给出了输入电压为3.3V、负载电流为4mA时,输入(VIN)纹波和输出(VOUT)纹波。

图5所示波形是当输出电流到达电流门限时RLIM引脚的电压波形。此时的电流门限设置在4mA,达到电流门限时,RLIM两端的电压为1.245V。

图5. APD电流为4mA时的APD输出(通道2)、VIN (通道3)以及APD电流监测输出(即RLIM两端电压) (通道4)。

效率测试

输入电压为3.3V和5V,负载电流在0至4mA范围变化时,对测试结果进行计算得到系统的整体效率,图6所示为70V输出条件下的效率曲线。

图6. 3.3V和5V输入时,效率与负载电流的对应关系曲线。

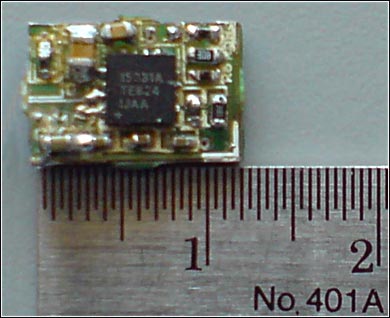

PCB设计

图7所示为参考设计布局,仅占用12mm x 8mm极小的电路板尺寸。图8和图9分别显示了顶层和底层元件布局。

图7. 参考设计电路板布局,尺寸为12mm x 8mm。

图8. 顶层元件布局

图9. 底层元件布局