MAXREFDES44#:采用1-WIRE ECDSA和XILINX ZYNQ SOC的安全认证设计

MAXREFDES44#为基于1-Wire®的安全认证参考设计,用于保护IP以及外设与Xilinx Zynq™ FPGA之间的安全认证。利用提供的示例代码,系统与DS28E35执行不对称质询-应答序列,以确保模块、外设或子系统的真实性。DS28E35通过Maxim Integrated的1-Wire总线通信。MAXREFDES44#配备有Pmod™连接器,以便利用Avnet MicroZed™立即进行测试。设计的简单性确保快速适应要求不对称ECDSA算法提供增强安全性的任何外设。

更多信息请参考详细资料标签页。包括原理图、PCB文件及物料单(BOM)在内的设计文件可从设计资源标签页下载。根据申请,在签署保密协议之后可提供固件。

注:对MAXREFDES44#进行编程要求单独购买DS28E35EVKIT#。

特性

- ECDSA安全认证

- 1-Wire接口

- 源代码示例

- Pmod兼容规格

竞争优势

- 强加密安全认证

- 带硬件加速,实现快速性能

- 外设安全认证不要求VCC引脚

应用

- 网络附加设备的安全认证(IoT)

- 严防假冒

- 外设安全认证

- IP保护

- 许可证与功能管理

详情介绍

概述

智能工厂以及工业和医疗应用充分利用了现代SoC的灵活性和高性能。随着这些系统的互联性越来越强,保护IP、跟踪产品生命周期以及防止造假等安全性问题也日益突出。MAXREFDES44#为基于1-Wire的非对称安全认证参考设计,用于对Xilinx SoC的外设进行安全认证。公钥储存在Xilinx SoC中,不占用安全密钥存储器位置;而私钥储存在采用DeepCover® 技术的DS28E35中。利用提供的示例代码,SoC与DS28E35执行质询-应答序列,确保模块、外设或子系统的真实性。DS28E35通过1-Wire总线通信,提供标准通信接口。图1所示的MAXREFDES44#硬件配备有Pmod兼容连接器,可使用Avnet MicroZed评估板随时进行测试。该设计非常简单,可快速用于任何要求使用不对称ECDSA算法实现增强安全性的外设。

图1. MAXREFDES44 DS28E35外设模块(顶面和底面)。

图1. MAXREFDES44 DS28E35外设模块(顶面和底面)。

硬件详细说明

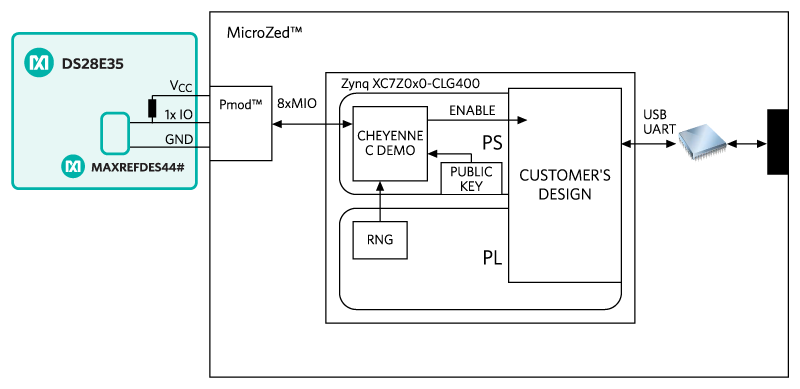

图2所示的硬件为设计上层的实现。系统要求为:

- Cheyenne ‘C’代码,运行在处理系统(PS)的ARM® Cortex® A9处理器。

- 加密安全伪随机数发生器(CSPRNG),运行在可编程逻辑(PL)

- PC,连接至RS-232端口(USB UART)

- MAXREFDES44#,带有DS28E35和680Ω上拉电阻

图2. 系统设计方框图

图2. 系统设计方框图

硬件

参考设计的硬件配置为:

- PC,1GB RAM

- Avnet MicroZed (Avnet提供,单独购买)

- Maxim DS28E35外设模块(提供MAXREFDES44#供购买)

- 可从设计资源标签页下载原理图、BOM和PCB Gerber

- USB-A至USB-micro B转换电缆

- Xilinx平台USB电缆

- DS28E35EVKIT#(第二代,带DS2475,单独购买),仅用于编程

软件

参考设计的软件要求为:

- Windows 7操作系统或更新

- 终端程序,例如Tera Term或HyperTerminal®

- Vivado®设计工具(Vivado 2014.2)

- 嵌入式设计工具(Xilinx SDK 2014.2)

- 固件文件

- 可在设计资源标签页的MAXREFDES44#产品着陆页申请,需签署保密协议(NDA):

- MAXREFDES44_NDA_FW.zip

- 可在设计资源标签页的MAXREFDES44#产品着陆页申请,需签署保密协议(NDA):

固件详细说明

Vivado项目文件包“MAXREFDES44.xpr.zip”包含详细的PS和PL。文件包采用基本Zynq配置,其中包含Avnet的MicroZed板定义(2014.2)和附加修改,增加了安全功能需要的CSPRNG。Avnet的MicroZed板定义(2014.2)可从其文档栏目下的MicroZed页面. Figure 3下载。图3所示的方框图位于“\MAXREFDES44.xpr\MZ_Zynq_HW”路径下,文件名为“MZ_Zynq_HW.xpr”。

图3. Zynq方框图。

图3. Zynq方框图。

PS和PL配置方框图如图4所示。

图4. PS-PL配置方框图。

图4. PS-PL配置方框图。

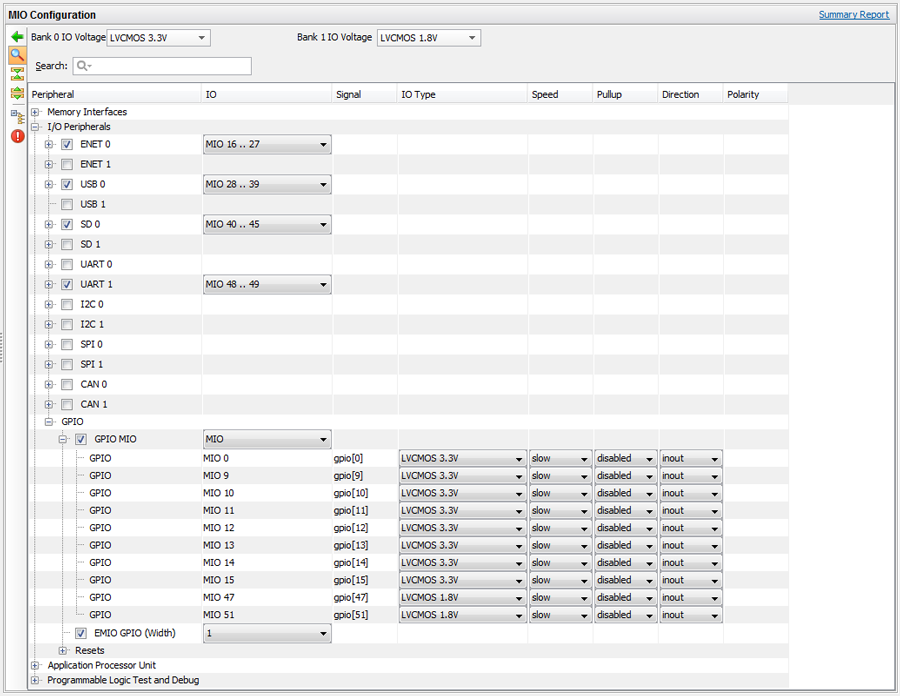

参考中使用的关键MIO配置为UART和GPIO接口,如图5所示。UART 1用于与终端程序通信,用于在MIO48(tx)和MIO49(rx)上输出外部打印命令。GPIO连接至MIO15 (1-Wire)和EMIO GPIO,宽度为1位,用于内部连接至CSPRNG (rng_top_0)。所有其它MIO配置为Avnet的MicroZed板定义的默认设置,该参考设计中不使用。

图5. Zynq MIO配置的示意图。

图5. Zynq MIO配置的示意图。

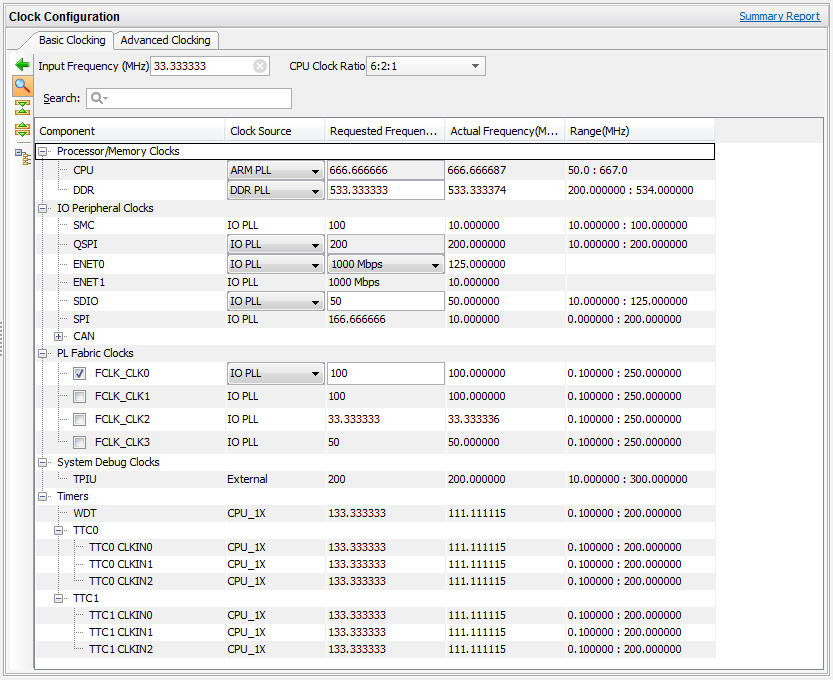

时钟配置设置为Avnet MicroZed板定义的默认值,但使能FCLK_CLK0信号,用于驱动CSPRNG,如图6所示。

图6. Zynq时钟配置示意图。

图6. Zynq时钟配置示意图。

CSPRNG为两个周期不同的环形振荡器输出的异或信号,被FCLK_CLK0信号采样来产生随机数。由于有两个环形振荡器,在PL上产生组合环,在构建设计时往往会发生错误。为克服错误并使其为警告,在执行完全构建之前,在tcl控制台上运行tcl文件“project_setup.tcl”。该文件位于路径“/MAXREFDES44/MZ_Zynq_HW”下。

快速入门

所需设备:

- Windows® PC,带两个USB端口

- MAXREFDES44#板

- MAXREFDES44#支持的平台(即MicroZed套件)

- 编程电缆(即平台USB II电缆或相当的电缆)

- DS28E35EVKIT#(第二代,带DS2475)

下载、阅读并严格按照MAXREFDES44#快速入门指南中的步骤执行。

1-Wire和DeepCover是Maxim Integrated Products, Inc的注册商标。

ARM是ARM Limited的注册商标和注册服务商标。

Cortex是ARM Limited的注册商标。

Eclipse是Eclipse Foundation, Inc的商标。

HyperTerminal是Hilgraeve, Incorporated的注册商标。

MicroZed是Avnet, Inc的商标。

Pmod是Digilent Inc的商标。

Vivado和Zynq是Xilinx, Inc的注册商标。

Windows是Microsoft Corporation的注册商标和注册服务商标。

Xilinx是Xilinx, Inc的注册商标和注册服务商标。