2-Channel ADC Measures Differential Temperature from Stacked Half Bridge Platinum RTD that Eliminates Half the Excitation Current and the Matching Requirements of a Full Bridge

详情介绍

概览

设计资源

驱动/参考代码

Software such as C code and/or FPGA code, used to communicate with component's digital interface.

优势和特点

- 四通道参数测量单元服务4个DUT

- 针对ATE应用进行设计

- 针对高精度进行优化

电路功能与优势

电路描述

- 每个PMU通道均有一个专用的ADC,从而可提供最快的吞吐速率和结果。

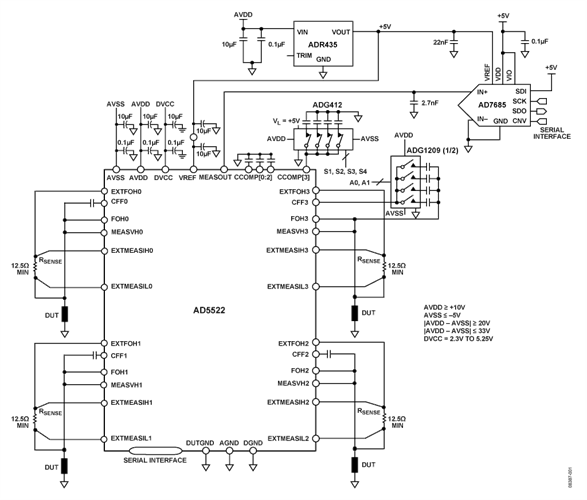

- 多个通道可共用一个ADC。图1中,四个PMU通道共用一个ADC AD7685。在一些应用中,可能有更多通道共用一个ADC,例如8个或16个PMU通道。

利用各MEASOUTx引脚的内部禁用功能,可以实现多个通道共用一个ADC。这就要求对PMU寄存器执行写入命令,以使能/禁用相应的开关。如果选择这种方法,则应注意,一次只能选择一个MEASOUTx通道。

或者,可利用外部4:1多路复用器来控制测量通道选择。以这种方式,可以使能所有四个MEASOUTx路径,由多路复用器选择测量通道。类似地,采用8:1或16:1多路复用器,可实现更多测量路径共享一个ADC。多路复用器的选择将取决于所用的ADC及其输入电压范围。对于双极性输入ADC, ADG1404/ ADG1204 系列器件将是理想之选;若采用单电源,则 ADG706 和 ADG708 更合适。除开关阻抗外,MEASOUTx路径的输出阻抗通常为60 Ω。因此,应考虑使用 ADA4898-1等ADC缓冲器来驱动ADC(图中未显示缓冲器)。

16位、250 kSPS ADC AD7685 能够处理MEASOUTx路径的0 V至4.5 V输出范围,所以适合本应用。此外,如果希望升级路径,速度更快但尺寸相同的其它ADC(例如16位、500 kSPS AD7686)也是颇具吸引力的选择。

如果需要20 V输出范围,则AD5522要求使用一个5 V基准电压源。选择5 V XFET基准电压源ADR435的原因在于,它具有低温度系数(A级为10 ppm/°C;B级为3 ppm/°C)、低噪声(8 μV峰峰值,0.1 Hz至10 Hz)以及能够驱动多个PMU通道(30 mA源电流,20 mA吸电流)特性。

一些应用要求PMU能够驱动各种大小的DUT电容,尤其在PMU与电源引脚相连,或者PMU用作器件电源,且存在DUT的去耦/旁路电容的应用中。这种情况下,将一个外部开关而不是固定电容与CCOMP引脚相连,可使附加CCOMP电容得以接通或断开,从而优化各种容性负载条件下的建立时间和稳定性。本电路所选的开关为四通道SPST开关ADG412,其导通电阻小于50 Ω。由于大多数多路复用器一次只允许接通多个通道中的一个通道,所以才选用四通道SPST开关,而不是多路复用器。利用四通道开关,各漏极可以连在一起,源极则可以与各补偿电容相连,从而提供24 − 1种可能的CCOMP组合。

同样,本电路采用差分多路复用器ADG1209 ,以适应与CFFx引脚相连、范围更宽的前馈电容,从而使AD5522能够驱动更宽范围的DUT电容。所用多路复用器的串联电阻应使得1/(2π × RON × CDUT) > 100 kHz。本例中,ADG1209用于切换AD5522的两个通道。

开关和电容将发生与AD5522 FOH引脚的电压范围相同的电压偏移。因此,开关和电容的额定电压应考虑这一点。CFF电容可以具有10%或以下的公差,这一额外变量会直接影响建立时间,特别是在低电流的测量电流模式下。所选的CCOMP电容公差应不大于5%。表1列出了不同负载电容下补偿电容CCOMP和CFF的建议标称值。

建议的补偿电容选择

| CLOAD | CCOMP | CFF |

| ≤1 nF | 100 pF | 220 pF |

| ≤10 nF | 100 pF | 1 nF |

| ≤100 nF | CLOAD/100 | CLOAD/10 |

本电路必须构建在具有较大面积接地层的多层电路板上。为实现最佳性能,必须采用适当的布局、接地和去耦技术(请参考教程MT-031——“实现数据转换器的接地并解开AGND和DGND的谜团”,以及 教程MT-101——“去耦技术”)。请注意,图1为原理示意图,并未显示所有必需的去耦。

精心考虑电源和接地回路布局有助于确保达到额定性能。安装AD5522所用的印刷电路板(PCB)应采用模拟部分与数字部分分离设计,并限制在电路板的一定区域内。如果AD5522所在系统中有多个器件要求AGND至DGND连接,则只能在一个点上进行连接。星形接地点尽可能靠近该器件。

图2:不同CCOMP值对应的输出电压步进响应(强制电压步进为11.25 V,负载为220 pF,使用ADG412 SPST开关)

图3:积分线性性能(使用AD7685测量FIMV误差,FI范围 = ±2 mA,测量输出增益 = 0.2)

图4:积分线性性能(使用AD7685测量FVMI误差,FV范围 = ±10 V,2 mA范围,5.6 kΩ负载)

图5:积分线性性能(使用AD7685测量FVMV误差,FV范围 = ±10 V,测量输出增益 = 0.2)

图6:积分线性性能(使用AD7685测量FIMI误差,FI范围 = ±2 mA,测量输出增益 = 0.2)

对于具有多个引脚 (AV SS 和 AV DD)的电源,建议将这些引脚连在一起,并且每个电源仅去耦一次。

AD5522应具有足够大的10 µF电源去耦电容,与每个电源上的0.1 µF电容并联,并且尽可能靠近封装,最好是正对着该器件。10 μF电容为钽珠型电容。0.1 µF电容应具有低有效串联电阻(ESR)和低有效串联电感(ESL)——高频时提供低阻抗接地路径的普通陶瓷型电容通常就是如此,能够处理内部逻辑开关所引起的瞬态电流。

应避免在该器件下方布设数字线路,否则会将噪声耦合至该器件。不过,可以将模拟接地层放在AD5522下方,以避免噪声耦合(此做法仅适用于焊盘朝上的封装)。AD5522的电源线路应采用尽可能宽的走线,以提供低阻抗路径,并减小电源线路上的突波效应。快速开关数字信号应利用数字地屏蔽起来,以免向电路板上的其它器件辐射噪声,并且绝不应靠近参考输入。必须将所有VREF线路上的噪声降至最低。

应避免数字信号与模拟信号交叠。电路板相反两侧上的走线应彼此垂直,以减小电路板的馈通效应。像所有薄型封装一样,必须避免弯曲封装,并且在组装过程中必须避免封装表面上出现点负载。

另外请注意,AD5522的裸露焊盘与负电源AVSS相连。

常见变化

PMU电路并非始终需使用AD5522的20 V完整输出范围,许多应用只需要其中的一部分。例如,用户使用2.5 V基准电压源ADR421 可以实现±5.6 V的标称输出电压范围,利用片内OFFSET DAC可进一步调整该范围,以适应DUT要求。(更多信息请参考AD5522 数据手册。)另外,能够使用较低供电轨也是额外的优势,特别是以每通道80 mA完整电流范围工作时,这有助于降低AD5522的功耗。

按ADC通道划分PMU测量通道有多种方式,多个PMU通道也可以共用一个ADC通道(有时以8:1或16:1的比率)。另外,也可以使用片内MEASOUT禁用功能或模拟多路复用器来实现。多路复用器会增加测量路径的串联电阻;因此,ADC输入端之前可能需要缓冲。

其它变化包括使用能够处理双极性信号范围的ADC,或者采样速率更快的ADC。

讨论

样片申请及购买

样片

| 产品 |

描述 |

可提供样片的 |

| ADR435 | 超低噪声XFET基准电压源,具有吸电流和源电流能力 | ADR435ARMZ ADR435ARZ ADR435BRMZ ADR435TRZ-EP |

| ADG412 | LC2MOS 精密四通道单刀单掷开关 | |

| AD5522 | 集成16位电平设置DAC的四参数测量单元 | |

| ADG1209 | 低电容、4通道、±15 V/+12 V iCMOS 多路复用器 | ADG1209YCPZ-REEL7 ADG1209YRUZ ADG1209YRZ |

| AD7685 | 16位、250kSPS PulSAR ADC,采用MSOP/QFN封装 | AD7685ACPZRL7 AD7685ARMZ AD7685BCPZRL7 AD7685BRMZ AD7685CCPZRL7 AD7685CRMZ |