Low Power 5V Battery Backup Supply with Autoswitchover and No Reverse Current

详情介绍

概览

设计资源

评估硬件

产品型号带"Z"表示符合RoHS标准。评估此电路需要下列选中的电路板

- EVAL-CN0251-SDPZ ($80.00) A Flexible 4-Channel Analog Front End for Wide Dynamic Range Signal Conditioning

- EVAL-SDP-CB1Z ($99.00) Eval Control Board

驱动/参考代码

Software such as C code and/or FPGA code, used to communicate with component's digital interface.

优势和特点

- 4通道宽动态范围

- 工业信号电平

- 提供高CMR的仪表放大器输入级

电路功能与优势

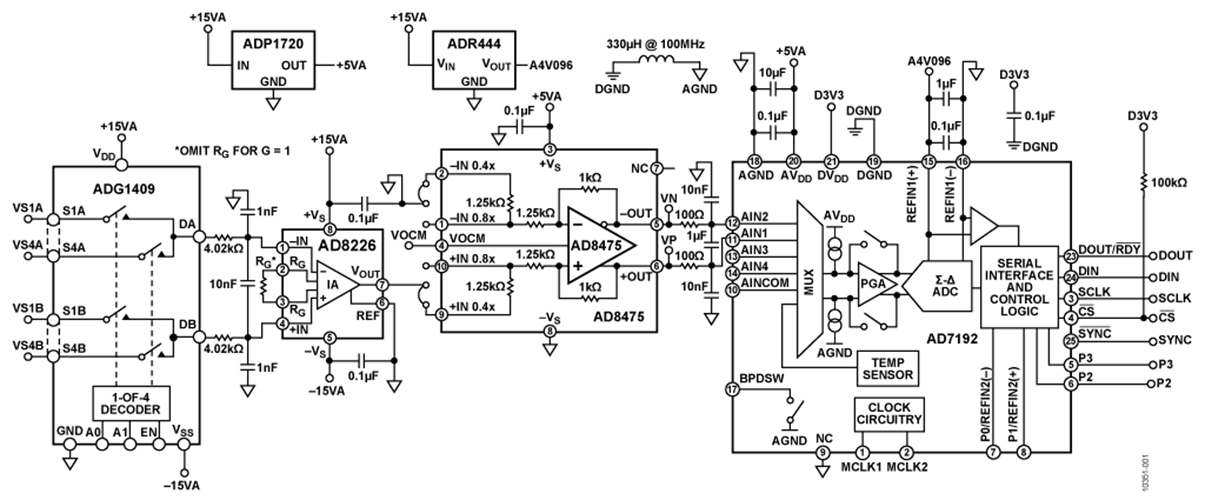

图1所示电路是一种灵活的信号调理电路,用于处理宽动态范围(从几mV p-p到20 V p-p)的信号。该电路利用高分辨率模数转换器(ADC)的内部可编程增益放大器(PGA)来提供必要的调理和电平转换并实现动态范围。

在过程控制和工业自动化应用中,±10 V满量程信号非常常见;然而,有些情况下,信号可能小到只有几mV。用现代低压ADC处理±10 V信号时,必须进行衰减和电平转换。但是,对小信号而言,需要放大才能利用ADC的动态范围。因此,在输入信号的变化范围较大时,需要使用带可编程增益功能的电路。

此外,小信号可能具有较大的共模电压摆幅;因此需要较高的共模抑制(CMR)性能。在某些源阻抗较大的应用中,模拟前端输入电路也需要具有高阻抗。

图1所示电路解决了所有这些难题,并提供了可编程增益、高CMR和高输入阻抗。输入信号经过4通道ADG1409 多路复用器进入 AD8226低成本、宽输入范围仪表放大器。AD8226低成本、宽输入范围仪表放大器。AD8226提供高达80dB的高共模抑制(CMR)和非常高的输入阻抗(差模800ΩM和共模400ΩM)。宽输入范围和轨到轨输出使得AD8226可以充分利用供电轨。

AD8475是一款全差分衰减放大器,集成精密增益电阻,可提供精密衰减(G=0.4或G=0.8)、共模电平转换及单端差分转换功能。AD8475是一种易于使用、完全集成的精密增益模块,采用单电源供电时,最高可处理±10 V的信号电平。因此,AD8475适用于衰减来自AD8226且最高20Vp-p的信号,同时维持高CMR性能并提供差分输出来驱动差分输入ADC。

AD7192是一款内置PGA的24位Σ-Δ型ADC。片内低噪声增益级(G = 1、8、16、32、64或128)意味着可直接向该ADC输入小信号。

结合上述器件,对幅度会变化的信号而言,该电路可以提供非常好的性能且易于配置。该电路适合工业自动化、过程控制、仪器仪表和医疗设备应用。

电路描述

该电路包含一个ADG1409多路复用器、一个AD8226仪表放大器、一个AD8475差动放大器、一个AD7192 Σ-Δ型ADC(使用ADR444基准电压源)以及 ADP1720稳压器。只需少量外部元件来提供保护、滤波和去耦,使得该电路具有高集成度,而且所需的电路板(印刷电路板[PCB])面积较小。

稳压器和基准电压源的选择

该电路选择ADP1720-5作为5 V稳压器。它是一款高压、微功耗、低压差线性稳压器,适合工业应用。

该电路选择4.096V ADR444作为基准电压源。它是一款超低噪声、高精度、低压差器件,特别适合高分辨率、∑-△型ADC和精密数据采集系统。

输入开关和保护

ADG1409 多路复用器拥有2位二进制地址线,可用于选择四种可能的输入通道之一。该设计还包括外部保护功能,如标准二极管和瞬态电压抑制器,用以增强电路的鲁棒性。这些在图1中并未显示,但是在CN0251设计支持包的详细原理图及其它文档中有所展示。

ADG1409多路复用器配置为接收四路差分输入信号:(VS1A−VS1B)、(VS2A−VS2B)、(VS3A−VS3B)和(VS4A−VS4B)。多路复用器的输出(DA和DB)施加于 AD8226仪表放大器的输入端。

AD8226输入仪表放大器

外部RG电阻设置D8226的增益。对于该电路,省略了RG,且仪表放大器级的增益为1。因此,AD8226的输出为VSxA–VSxB,其中x为输入通道编号。

AD8226的差分输入由两个4.02k电阻和一个10nF电容进行滤波,这些电阻和电容构成一个截止频率为2.0kHz的单极点RC滤波器。两个1nF电容增加了截止频率为40kHz的共模滤波。

AD7192ADC PGA增益配置

AD7192配置为接收差分模拟输入,以匹配来自AD8475的差分输出信号。AD7192的满量程输入范围为±VREF/增益,其中±VREF=REFINx(+)-REFINx(-)。

AD7192中的缓冲器使能时,输入通道会驱动缓冲放大器的高阻抗输入级,此模式下的绝对输入电压范围将限制在AGND+250mV至AVDD-250mV。增益级使能后,缓冲器输出将施加于PGA的输入端,模拟输入范围必须限制在±(AVDD-1.25V)/增益以内,因为PGA需要额外的裕量。因此,采用4.096V基准电压源和5V电源时,为了最充分地利用ADC的动态范围,可按表1所示对信号进行衰减或放大。

表1. AD8475和 AD7192内置PGA的各种输入范围增益配置

| 输入范围(VSxA − VSxB) |

AD8475增益 | AD7192增益 | PGA输出范围,双极性模式(V) |

| ±10 V | 0.4 | 1 | ±4 |

| ±5 V | 0.8 | 1 | ±4 |

| ±1 V | 0.4 |

8 | ±3.2 |

| ±500 mV | 0.8 | 8 | ±3.2 |

| ±250 mV | 0.8 | 16 |

±3.2 |

| ±125 mV | 0.8 | 32 |

±3.2 |

| ±62.5 mV | 0.8 | 64 | ±3.2 |

| ±31.25 mV | 0.8 | 128 | ±3.2 |

差分衰减放大器

为了驱动低压ADC,±0V或±5V信号需要进行衰减和电平转换。若将差动放大器配置与精密电阻配合使用,势必会因电阻之间出现失配而导致CMR性能下降。AD8475电平转换器/衰减器集成精密激光调整匹配电阻,可确保低增益误差、低增益漂移(最大33ppm/°C)和高CMR特性。

AD8475提供两个引脚可选的增益选项,即0.4和0.8。VOCM引脚用于调整精密电平转换的输出共模电压,以便匹配ADC的输入范围,并使动态范围最大化。此引脚可保持悬空,并利用一个精密分压器进行内部偏置,该分压器由电源与地之间的两个200M电阻组成,从而在该引脚上提供中间电源电压。

由两个100电阻和一个1F电容组成的一个单极点差分RC滤波器充当AD7192的抗混叠和降噪滤波器,其截止频率为800Hz。两个10nF电容提供截止频率为160kHz的共模滤波。

滤波器、输出数据速率和建立时间

AD7192 Σ-Δ型ADC由调制器和数字滤波器组成。输出数据速率(fADC)和建立时间(tSETTLE)与滤波器配置及斩波配置有关。表2显示了不同配置情况下的输出数据速率和建立时间计算情况。

表2. 不同配置的输出数据速率和建立时间

| 斩波滤波器选项 | SINC3 | SINC4 |

| 禁用 | fADC = fCLK/(1024 × FS[9:0]) tSETTLE = 3/fADC

|

fADC = fCLK/(1024 × FS[9:0]) tSETTLE = 4/fADC

|

| 使能 | fADC = fCLK/(3 × 1024 × FS[9:0]) tSETTLE = 2/fADC

|

fADC = fCLK/(4 × 1024 × FS[9:0]) tSETTLE = 2/fADC |

布局考虑

该电路或其它任何高速/高分辨率电路的性能都高度依赖于适当的PCB布局,包括但不限于电源旁路、信号路由以及适当的电源层和接地层。有关PCB布局的详情,请参见指南 MT-031 和 MT-101以及“ 高速印刷电路板布局实用指南”一文。

系统性能

24位 AD7192 Σ-Δ 型ADC可在该电路中提供非常好的性能。有关Σ-Δ 型ADC的更多详情, 请参见指南 MT-022 和 MT-023。

在配置设为斩波禁用、输出数据速率为4.7 Hz、增益为1且采用一个SINC4滤波器的情况下,噪声性能如图2所示,500个样本的噪声分布直方图则如图3所示。该电路中测得的峰峰值噪声约为3.9 μV(见图2),均方根噪声为860 nV。这相当于峰峰值(无噪声码)分辨率为20位,均方根分辨率为23位。表3显示了斩波禁用且采用一个SINC4滤波器时一些数据速率和增益设置条件下的AD7192均方根噪声。

图2. 噪声输出(VREF = 4.096 V, AVDD = 5 V, Output Data Rate = 4.7 Hz, a Rate = 4.7 Hz,

图3. 噪声直方图(VREF = 4.096 V,AVDD =5 V,输出数据速率 = 4.7Hz,增益 = 1,斩波禁用,SINC4滤波器)

表3. 斩波禁用且采用一个SINC4滤波器时不同输出数据速率和增益设置条件下的AD7192系统均方根分辨率(减去2.7位以获取峰峰值或无噪声码分辨率)

| 滤波器字(十进制) | 输出数据速率(Hz) | 建立时间(ms) | 增益 1 | 增益 8 | 增益 16 | 增益 32 | 增益 64 | 增益 128 |

| 1023 | 4.7 | 852.5 | 23.0 | 21.8 | 20.4 | 19.7 | 18.8 | 17.4 |

| 640 | 7.5 | 533 | 22.5 | 21.5 | 20 | 19.5 | 18.5 | 17.2 |

| 96 | 50 | 80 | 22.3 | 20.9 | 19.8 | 19.3 | 18.2 | 17 |

| 16 | 300 | 13.3 | 21.8 | 20.2 | 19.3 | 18.6 | 17.6 | 16.8 |

| 5 | 960 | 4.17 | 20.9 | 19.8 | 18.9 | 18 | 17.2 | 16.2 |

| 1 | 4800 | 0.83 | 19.2 | 19.0 | 18.4 |

17.6 | 16.6 | 15.8 |

电路评估与测试

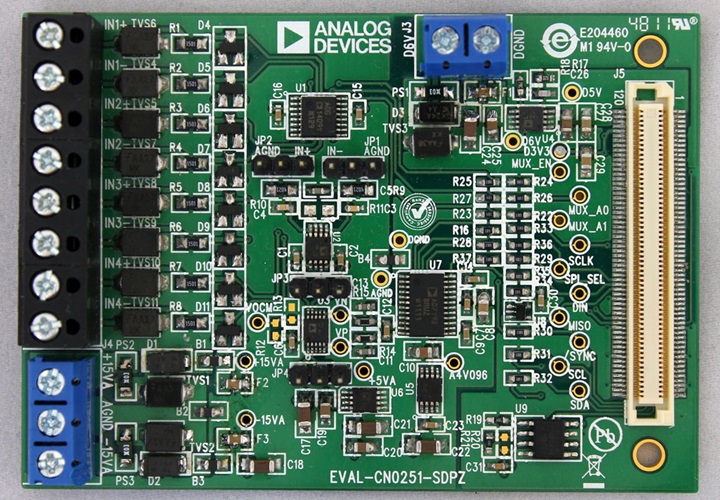

该电路测试设置使用 EVAL-CN0251-SDPZ电路评估板和系统演示平台(SDP)评估板( EVAL-SDP-CB1Z)。这两片板具有120引脚的对接连接器,可以快速完成设置并评估电路性能 EVAL-CN0251-SDPZ 板包含要评估的电路,如本电路笔记所述;SDP评估板与CN-0251 评估软件一起使用,可从 EVAL-CN0251-SDPZ 中获取数据。SDP也用于控制 AD7792 ADC中的多路复用器输入和各种功能。

设备要求

需要以下设备:

- 带USB端口的Windows XP、Windows Vista(32位)或Windows 7(32位)PC。

- EVAL-CN0251-SDPZ 电路评估板。

- EVAL- SDP-CB1Z SDP评估板。

- 直流电源:+15 V、-15 V和+6 V。

- CN-0251评估软件。

开始使用

将 CN-0251 评估软件光盘放进PC的光盘驱动器,加载评估软件。找到包含评估软件光盘的驱动器,打开Readme文件。按照Readme文件中的说明安装和使用评估软件。

功能框图

图4为测试设置功能框图。EVAL-CN0251-SDPZ-SCH.pdf文件包含EVAL-CN0251-SDPZ的详细原理图。此文件位于CN-0251设计支持包中:www.analog.com/CN0251-DesignSupport

图4. 测试设置功能框图

设置

将 EVAL-CN0251-SDPZ 上的120引脚连接器连接到 EVAL-SDP-CB1Z (SDP) 上的CONA连接器。使用尼龙五金配件通过120引脚连接器两端的孔牢牢固定这两片板。将直流输出电源成功设置为+15 V、-15 V和+6 V输出后,关闭电源。

在断电情况下,将+15 V电源连接到J3的+15VA引脚,将-15V电源连接到J3的-15VA引脚,将GND连接到J3的AGND引脚。此外,在断电情况下,将6 V电源连接到J2。接通电源,然后将SDP板附带的USB电缆连接到PC上的USB端口。接通 EVAL-CN0251-SDPZ 的直流电源之前,请勿将该USB电缆连接到SDP板上的微型USB连接器。

测试

设置好电源并将它连接到 EVAL-CN0251-SDPZ 后,启动评估软件,并通过USB电缆将PC连接到SDP板上的微型USB连接器。如果设备管理器中列出了Analog Devices SystemDevelopment Platform驱动器,软件将能与SDP板通信。

一旦USB通信建立,就可以使用SDP来发送、接收和捕捉来自 EVAL-CN0251-SDPZ 的串行数据。然后,连接信号源以便进行测量。

有关SDP的信息,请访问 www.analog.com/SDP。

讨论

样片申请及购买

样片

| 产品 |

描述 |

可提供样片的 |

| ADG1409 | 4 Ω导通电阻、4/8通道、±15 V/+12 V/±5 V iCMOS多路复用器 | ADG1409SRUZ-EP ADG1409YCPZ-REEL7 ADG1409YRUZ |

| ad7192 | 4.8 kHz、超低噪声、24位、Σ-Δ型ADC,内置PGA | AD7192BRUZ |

| AD8226 | 宽电源电压范围、轨到轨输出仪表放大器 | AD8226ARMZ AD8226ARZ |

| AD8475 | 精密、可选增益、全差分漏斗放大器 | AD8475ACPZ-R7 AD8475ARMZ AD8475BRMZ |

| ADP1720 | 50 mA、高压、微功耗线性稳压器 | ADP1720ARMZ-3.3-R7 ADP1720ARMZ-5-R7 ADP1720ARMZ-R7 ADP1720TRMZ-EP ADP1720TRMZ3.3-EP ADP1720TRMZ5-EP |

| ADR444 | 超低噪声、4.096V LDO XFET®基准电压源,具有吸电流和源电流能力 | ADR444ARMZ ADR444ARZ |

- 加入我的myAnalog 登录 myAnalog