2-Channel ADC Measures Differential Temperature from Bridge Configured RTDs that Eliminates Drop in Connecting Wire

详情介绍

概览

设计资源

优势和特点

- 将RF频率下变频至基带

- 采用双通道进行IQ解调

- 在高增益和高频率状态下工作时具有出色的SFDR

电路描述

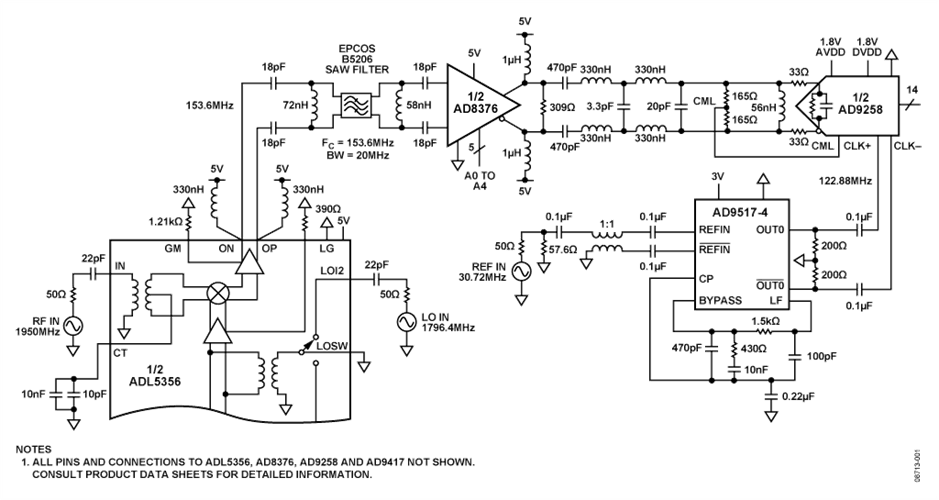

本电路包括RF前端和IF采样接收机,由双通道平衡混频器、宽带IF SAW滤波器、数字控制双通道VGA和双通道ADC组成。本电路还内置频率合成器,用来产生ADC采样时钟。

双通道平衡混频器ADL5356旨在将主要在1200 MHz至2500 MHz范围内的射频(RF),下变频为30 MHz至450 MHz范围内的低中频(IF)。

RF 和LO 输入端口已进行交流耦合,用来预防非零直流电压 损坏RF 巴伦或LO 输入电路(ADL5356 的一部分)。ADL5356 配置为单端LO 工作模式,建议LO 驱动为0 dBm。混频器的 LOSW 引脚接地,本电路只使用两个LO 通道中的一个(LOI2)。

混频器差分IF 接口需要利用上拉扼流圈电感来偏置开集输出, 并设置输出阻抗匹配。应适当选择用来将直流电流耦合至IF 放大器的扼流圈电感的分流阻抗,以提供所需的输出回损。混 频器输出阻抗的实部约为 200 Ω, ,这与许多常用SAW 滤波器 匹配,而无需变压器。

接收机通道滤波主要由混频器后接的153.6 MHz、20 MHz带宽 Epcos B5206 型SAW滤波器完成。此滤波器的典型插入损耗(IL) 约为9 dB,匹配特性阻抗为100 Ω 差分。通过简单的L-C电抗 性网络,使该SAW滤波器与混频器 200 Ω 差分输出和AD8376 VGA 150 Ω 差分输入阻抗相匹配。

表1突出显示了双通道混频器加SAW滤波器的级联性能。请注 意,IP3 为三阶交调截点,IP1dB为折合到输入端的−1 dB压缩 点,NF为噪声系数。

表1. 双通道混频器加SAW 滤波器的级联性能(RF =1950 MHz,LO = 1796.4 MHz,IF = 153.6 MHz,RF 功率 = -10 dBm, LO 功率 = 0 dBm)

| Gain (dB) | IP3 (dBm) | IP1dB (dBm) | NF (dB) | |

| ADL5356 | 8.2 | 30.0 | 11.5 | 9.7 |

| ADL5356 + SAW | -0.3 | 28.6 | 11.7 | 10.9 |

双通道、高输出线性VGA AD8376针对ADC接口进行了优化, 提供24 dB的接收机增益控制。两个独立的5 位二进制码以1 dB步进改变各衰减器的设置,使得各放大器的增益设置范围 为+20 dB至−4 dB。在可用的24 dB增益范围内,输出三阶交 调截点(IP3)和本底噪声基本上保持不变。对于接收机增益改 变时需保持恒定瞬时动态范围的可变增益接收机而言,这一 特性很重要。采用2 V峰峰值复合信号时,AD8376 和随后的 抗混叠滤波器的输出IP3 超过50 dBm。

AD8376 提供150 Ω输入阻抗,经过调整,用于驱动150 Ω 负载阻抗。开集输出结构要求通过外部偏置网络实现直流偏 置。每个通道输出端均采用一组1 μH扼流圈电感,用来向开 集输出引脚提供偏置。模数转换之前的DGA 输出端配有经过优化的差分四阶带通抗混叠滤波器。请注意,抗混叠滤波器 采用大约300 Ω.的分流输入和输出电阻端接。滤波器输入端 的分流电阻为 309 Ω 输出端的分流电阻为330 Ω (由两个 165 Ω 偏置设置电阻组成) 二者共同向AD8376 提供150 Ω 标称负载阻抗。

带通抗混叠滤波器用来衰减奈奎斯特频率区域之外的 AD8376 输出噪声。一般而言,若使用一个阶数合适的抗混 叠滤波器,SNR性能会提高数个dB。该抗混叠滤波器由一个 四阶巴特沃兹滤波器和一个谐振回路组成。谐振回路通过谐 振消除ADC负载的容性部分,有助于确保ADC输入在目标中 心频率看起来像一个真正的电阻(参见应用笔记AN-742和 AN-827)。此外,交流耦合电容和偏置扼流圈会将更多零点 引入传递函数。整体频率响应呈现出带通特性,有助于抑制 目标奈奎斯特频率区域外的噪声。该滤波器提供20 MHz通 带,中心频率为153.6 MHz,平坦度为0.3 dB,插入损耗约 为3 dB。

所用ADC为14 位 AD9258, 其采样速率最高可达125 MSPS。 AD9258 的模拟输入端由AD8376 通过带通抗混叠滤波器驱 动。ADC采样速率设置为122.88 MSPS,满量程输入范围为 2 V峰峰值。AD9258 差分时钟信号由一个带片内VCO的时钟 产生IC AD9517-4 提供。为实现低抖动,使用LVPECL电平输 出OUT0。 AD9517-4利用其内部VCO频率1474.56 MHz,产 生用于ADC的122.88 MHz输出时钟。利用ADISimCLK™仿 真软件设计的环路滤波器提供60 kHz截止频率和50°相位余 量,使得时序抖动约为160 fs均方根值。假设输入频率为153.6 MHz,利用公式SNR = 20 log(1/2π × f IN × t j).

利用此电路,在最大增益时可实现79.61 dBc的出色SFDR性 能(153.6 MHz),如图2所示。

常见变化

前端LNA和衰减器未包括在本电路中,但可以轻松地与混频器ADL5356的50 Ω单端RF输入接口。完整的接收机设计可能需要纳入ADL5521/ADL5523 LNA

标准配置使用ADL5356,可以接收1.2 GHz至2.4 GHz范围内的RF信号,但也可以使用混频器ADL5358,支持500 MHz至1700 MHz的RF输入频率。

Epcos (www.epcos.com) SAW滤波器接在混频器之后,提供必要的通道选择功能,带宽范围为20 MHz至40 MHz,具体取决于所选的滤波器。所示电路使用20 MHz带宽、153.6 MHz中心频率SAW滤波器(产品型号:B5206),但也可以使用其它引脚兼容的滤波器。

在SAW滤波器匹配和抗混叠滤波器实施方案中,可能还需要考虑一些经验优化方法,帮助补偿实际的PCB寄生效应。关于级间滤波器设计的详细信息,请参考应用笔记 关于AVDD和DVDD电源的正确时序(如果使用独立的电源),应参考相应的ADC数据手册。AN-742 和 AN-827

为确保频带响应的可重复性,SAW滤波器匹配元件和抗混叠滤波器建议使用1%电容。此外,推荐使用Coilcraft 0603CS或类似的电感。其它电阻、电容和电感的精度可以为10%。

为了使本文所讨论的电路达到理想的性能,必须采用出色的布线、接地和去耦技术。至少应采用四层PCB:一层为接地层,一层为电源层,另两层为信号层。

所有IC电源引脚都必须采用0.01 μF至0.1 μF的低电感多层陶瓷电容(MLCC)去耦至接地层(为简明起见,图中未显示),并应遵循各数据手册和MT-101的相关建议。

有关布线方式和关键器件定位的建议,请参考产品评估板,可以通过器件的产品页面查询评估板。

即使AD8376和AD9258(或其它ADC)采用不同电源供电,因为ADC的输入信号为交流耦合信号,所以时序控制也不是问题。

关于AVDD和DVDD电源的正确时序(如果使用独立的电源),应参考相应的ADC数据手册。).