Terasic DE2i-150 Cyclone IV Board

详情介绍

电路描述

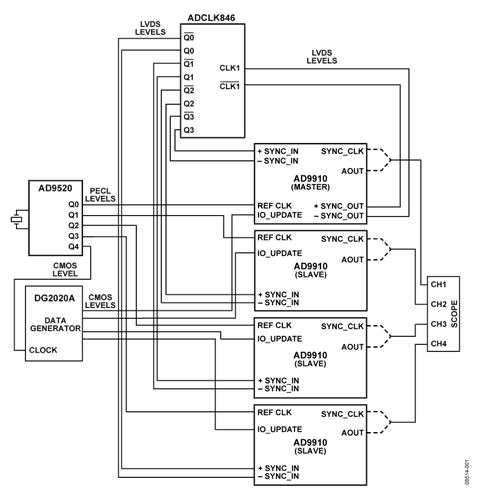

图1所示电路由各产品的评估板相连构成。连接所用的电缆长度相互匹配。同步多个AD9910有三项基本要求,首先要求提供完全一致的参考时钟(REF CLK)。

该设置将AD9520用作各AD9910 DDS的参考时钟源。AD9520利用外部晶振和内部PLL工作,将相位对准的1 GHz参考时钟(PECL输出)分配给所有四个AD9910评估板。它还向Tektronix DG2020A数据模式发生器提供CMOS输出时钟,用于IO_UPDATE。

其次要求对准所有四个AD9910的SYNC_CLK上升沿。SYNC_CLK提供基准,以便实现完全一致的IO_UPDATE。SYNC_CLK对准利用AD9910的内部同步功能实现。ADCLK846向所有四个AD9910分配相位对准的SYNC_IN。有关AD9910同步功能的更多详细信息,请参考其数据手册。

图2显示AD9910内部同步电路禁用时的所有四个SYNC_CLK。请注意,即使参考时钟相位对准,SYNC_CLK本身也不一定会对准。

为使SYNC_CLK上升沿相位对准,将一个AD9910设置为主器件,将其它DDS设置为从器件。主器件的SYNC_OUT为LVDS信号,由ADCLK846缓冲并分配给所有AD9910评估板。SYNC_IN信号(LVDS)必须满足各器件系统时钟的内部设置与保持时间要求。AD9910还能够延迟主器件的SYNC_OUT,以便达到这一时序要求。为了提高灵活性,各器件的内部SYNC_IN路径均可独立延迟。

图2. SYNC_CLK未对准

在图1所示设置中,评估板之间的连接采用匹配电缆,因此可以使用内部默认延迟值来实现SYNC_CLK相位对准。图3显示通过上述同步程序而实现的SYNC_CLK相位对准。

最后,同步多个DDS器件要求IO_UPDATE完全一致。IO_UPDATE必须满足SYNC_CLK的设置与保持时间要求。图1所示的IO_UPDATE同步发送至SYNC_CLK。最后一项要求使DDS输出可控。

图4和图5显示相位对准的DDS输出。由于这些器件彼此同步,因而DDS之间的相位和/或幅度调整可预测。

请注意,图5中的系统时钟工作频率降至100 MHz,并且输出未经滤波,可显示各DDS的原始输出。图5还显示各器件输出相同信号时的同步值。

图3. SYNC_CLK已对准

图4. 采用图1所示设置、相位对准且经过滤波的DDS输出

图5. 采用图1所示设置、相位对准且未经过滤波的DDS输出

常见变化

ADI提供各种直接数字频率合成器、时钟分配芯片和时钟缓冲器,用来构建基于DDS的时钟发生器。欲了解更多信息,请访问www.analog.com/zh/dds 和 www.analog.com/zh/clock 。