Altera 100G Development Kit, Stratix V Edition

详情介绍

概览

设计资源

评估硬件

产品型号带"Z"表示符合RoHS标准。评估此电路需要下列选中的电路板

- EVAL-CFTL-6V-PWRZ ($17.00) Universal Power Supply

- EVAL-CN0270-EB1Z ($145.00) Complete 4 mA to 20 mA HART Solution

驱动/参考代码

Software such as C code and/or FPGA code, used to communicate with component's digital interface.

优势和特点

- 完整的HART解决方案

- 4 mA至20 mA

- 业界功耗最低

电路功能与优势

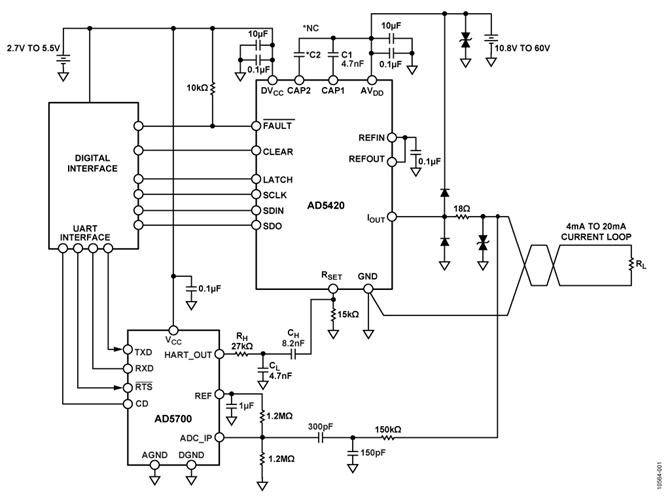

图1所示电路使用 AD5700 (业界功耗最低、尺寸最小的HART1兼容型IC调制解调器) 以及AD5420 (一款16位电流输出DAC),形成完整的HART兼容型4 mA至20 mA解决方案,这在环路供电变送器的应用中非常常见。

为了进一步节省空间, AD5700-1 提供了精度为0.5%的内部振荡器。

图1. AD5420 HART使能电路简化原理图

该电路符合由HART通信基金会定义的HART物理层规范,例如模拟变化率和静默期间噪声规格。

多年来,过程控制仪器仪表中一直使用4 mA至20 mA通信。此通信方式稳定可靠,对长距离通信中的环境干扰具有高抗扰度。不过,其限制是每次只能进行一个过程变量的单向通信。

可寻址远程传感器高速通道(HART)标准的开发实现了高性能的双向数字通信,同时支持传统仪器仪表设备所使用的4 mA至20 mA模拟信号。它衍生出各种特性,例如远程校准、故障查询和额外过程变量的传输。简言之,HART是一种数字双向通信系统,其在4 mA至20 mA模拟电流信号之上调制一个1 mA p-p频移键控(FSK)信号。

电路描述

图2. AD5700/AD5700-1样片调制器波形

确定外部元件值

C1和C2可配合器件的数字压摆率控制功能使用,以控制AD5420对应的IOUT信号的压摆率。确定电容的绝对值时,要确保调制解调器的FSK输出无失真通过。因此,调制解调器输出信号的带宽必须通过1200 Hz和2200 Hz频率。图3显示了实现此要求的电路。在此情况下C2保持开路。

图3. AD5420/AD5410和AD5700 HART调制解调器连接

低通和高通滤波器电路通过R H、C L、 C H和 C1的相互作用并配合AD5420的一些内部电路来形成。在计算这些元件的值时,低通和高通频率截止点目标分别为>10 kHz和<500 Hz。图4显示了仿真频率响应的曲线图,表1显示了增加各元件值而剩余元件值保持不变对频率响应的影响。

表1. 个别频率响应的影响

元件值增加

| 元件 | C1 | CH |

CL | RH |

| fL(Hz) | ↓ | ↓ | ↓ | ↓ |

| fH(kHz) | ↓ | 无变化 |

无变化 | 无变化 |

| G(dB) | ↓ | ↑ | ↓ | ↓ |

调制解调器的输出是一个FSK信号,包括1200 Hz和2200 Hz移频。这个信号需要转换为1个1 mA峰峰值电流信号。为此,RSET引脚上的信号幅度必须衰减。这是因为AD5420有内部电流增益配置设计。假定调制解调器的输出幅度为500 mV峰峰值,则其输出必须经过500/150 = 3.33倍衰减。此衰减通过RH 和 CL来实现。

本电路笔记中的测量使用以下元件值完成:

- C1 = 4.7 nF

- RH = 27 kΩ

- CL = 4.7 nF

- CH = 8.2 nF

图5是在500 Ω负载电阻上分别测得了1200 Hz和2200 Hz移频。通道1显示耦合至AD5420输出中的调制HART信号(设置为输出4 mA),而通道2显示AD5700 TXD信号。

图5. 在500 Ω负载上测得的FSK波形

HART兼容性

图1中的电路要与HART兼容,必须符合HART物理层规范。HART规范文档中包含了众多物理层规范。其中最重要的两个是静默期间的输出噪声和模拟变化率。

静默期间的输出噪声

当HART设备没有进行传输(静默)时,不应在HART扩展频带中有噪声耦合到网络上。噪声过高可能会干扰设备本身或网络上的其它设备对HART信号的接收。

对于在500 ¬负载上测得的电压噪声,其包含的扩展频带中的宽带噪声和相关噪声总和不超过2.2 mV rms。此噪声通过在500 Ω负载上连接HCF_TOOL-31滤波器(可从HART通信基金会获得)并将滤波器输出连接到真均方根测量仪(参见图6)来测量。也可使用示波器来检查输出波形峰峰值电压。

AD5420输出电流设置为4 mA、12 mA和20 mA。测得噪声没有明显差异。使用和不使用HCF_TOOL-31带通滤波器时,测得的均方根值分别为115 μV rms和252 μV rms。这两个值均在要求的2.2 mV rms(使用HART滤波器)和138 mV rms(不使用HART滤波器的宽带噪声)规范内。

图6. HART规范测试电路

图7和图8分别显示4 mA和12 mA输出电流的示波器曲线图。请注意,滤波器的通带增益为10。通道1和通道2分别显示滤波器的输入和输出。

图7. HART滤波器输入(通道1)和输出(通道2)端的噪声,输出电流为4 MA

图8. HART滤波器输入(通道1)和输出(通道2)端的噪声,输出电流为12 MA

模拟变化率

此规范可确保当设备调节电流时,模拟电流的最大变化率不会干扰HART通信。电流的阶跃变化是会扰乱HART信号。仍然使用如图6所示的相同测试电路。为进行这个测试,AD5420编程输出一个4 mA至20 mA切换的周期波形,并且该波形在两个值上都没有延迟,以获得最大变化率。为了符合HART规范,滤波器输出端的波形的峰值电压不能大于150 mV。符合这一要求可确保模拟信号的最大带宽处于规定的直流至25 Hz频带中。

AD5420输出从4 mA变为20 mA的通常时间约为10 μs。这个速度显然太快,而且会对HART网络造成重大破坏。为了降低变化率,AD5420提供了两种特性:一是在CAP1和CAP2引脚处连接电容,二是提供数字压摆率控制功能(详情请参考AD5420数据手册 )。

要使带宽降低到25 Hz以下,需要在CAP1和CAP2引脚处连接非常大的电容值。最佳解决方案是结合外部电容和AD5420的数字压摆率控制功能。两个电容C1和C2的作用是降低模拟信号的变化率;不过还不足以满足规范。使能压摆率控制功能可以为变化率的设置提供灵活性。

图9. AD5420输出(通道1)和HART滤波器输出(通道2),SR CLOCK = 3,SR STEP = 2,C1 = 4.7 NF,C2 = NC

图9显示AD5420的输出和HART滤波器的输出。滤波器输出端的峰值电压为80 mV,处于规定范围以内。压摆率设置为SR CLOCK = 3和SR STEP = 2,从4 mA至20 mA的转换时间设为约120 ms,C1 = 4.7 nF,C2未连接。如果这个变化率太慢,可以减少压摆时间。但这会使滤波器输出端的峰值电压增加。从CAP1连接至AVDD 的电容可用于抵消此增加。

图10显示了压摆率控制设置改为SR CLOCK = 5和SR STEP = 2,同时C1电容值保持4.7 nF不变的结果。这样,转换时间就会在240 ms左右。滤波器输出端的峰值幅度可通过增加C1值、或配置更慢的压摆率或通过两者的组合来进一步降低。

图10. AD5420输出(通道1)和HART滤波器输出(通道2),SR CLOCK = 5,SR STEP = 2,C1 = 4.7 NF,C2 = NC

瞬变电压保护

AD5420内置ESD保护二极管,在一般工作条件下可防止器件受损。但是,工业控制环境会使I/O电路遭受高得多的瞬变。为了防止过高瞬态电压影响AD5420,可能需要外部功率二极管和浪涌电流限制电阻,如图1所示。对电阻值的约束条件(图1中显示为18 Ω)是,在正常工作期间,IOUT 的输出电平必须保持在其电压限值(AVDD )以内,并且这两个保护二极管和电阻必须具有适当的额定功率。在18 Ω下,对于4 mA至20 mA输出,引脚上的电压限值会降低V = IMAX × R = 0.36 V。还可以通过瞬态电压抑制器(TVS)或瞬态吸收器可实现进一步的保护。这些元件包括单向和双向抑制器,可提供各种各样的隔离和击穿电压额定值。TVS应尽量采用最低击穿电压定标,同时在电流正常输出的范围内不导通。建议保护所有远程连接节点。

在许多过程控制应用中,需要在控制器与受控单元之间提供一个隔离栅,以保护和隔离控制电路遭受可能发生的任何危险的共模电压。ADI公司的iCoupler 系列产品可提供超过2.5 kV的电压隔离。有关iCoupler产品的更多信息,请访问www.analog.com/icouplers。为了减少所需隔离器的数量,CLEAR等非关键信号可以连到GND;FAULT 和SDO可以不连接,从而只需要隔离三个信号。不过请注意,FAULT 或SDO引脚是访问AD5420的故障检测功能所必需的。

常见变化

图1所示电路的一个常见变化是使用AD5422(LFCSP版本),它类似于AD5420,但具有电压输出通道和电流输出通道,因而是PLC/DCS类应用的常见选择。电路笔记CN-0065 提供有关IEC 61000兼容解决方案的额外信息,该解决方案适合使用AD5422和ADuM1401 数字隔离器的全隔离式输出模块。电路笔记 CN-0233 包含有关提供电源和数据隔离的信息,所使用的是ADuM3471 PWM 控制器和具有四通道隔离器的变压器驱动器。

如果需要多个通道,可使用AD5755-1 四通道电压和电流输出DAC。该产品具有创新型片内动态电源控制功能,在电流模式下,可以最大限度地降低封装功耗。各通道均有一个相应的CHART引脚,因此HART信号可以耦合到AD5755-1的电流输出端。

如果需要环路供电的4 mA至20 mA HART解决方案,可以组合AD5421 和AD5700 HART调制解调器。

电路评估与测试

要构建此电路,需要使用AD5420评估板(EVAL-AD5420EBZ) 和AD5700-1评估板 (EVAL-AD5700-1EBZ),参见图11。除外两个评估板,该电路还需要三个外部电容(C1、 CH和CL)、一个负载电阻(RL)和一个UART接口。

设备要求

- AD5420评估板(EVAL-AD5420EBZ)

- AD5700评估板(EVAL-AD5700-1EBZ)

- 运行Windows® XP的PC,带USB端口

- 主机控制器和UART接口(标准微控制器,例如ADuC7060)

- 电源电压:10.8 V至60 V

- 数字测试滤波器(HCF_TOOL-31,可从HART通信基金会获得)

- 500 Ω负载电阻

- 外部电容,C1 (4.7 nF)、CH (8.2 nF)、CL (4.7 nF);一个电阻,RH (27 kΩ)

- 示波器,Tektronix DS1012B或等效器件

图11. 测试设置框图

对于静默测试期间的输出噪声,如上所述,AD5700调制解调器不发射数据(静默)。AD5420设置为输出所需的电流并通过HCF(HART通信基金会)带通滤波器。接着使用Tektronix TDS1012B示波器测量输出噪声。

模拟变化率规范可确保当AD5420调节电流时,模拟电流的最大变化率不会干扰HART通信。电流的阶跃变化会扰乱HART信号传输。

为进行这个测试,AD5420编程为输出一个4 mA至20 mA切换的周期波形,并且该波形在两个值上都没有延迟,以获得最大变化率。所用的压摆率设置为SR CLOCK = 3和SR STEP = 2,C1设置为4.7 nF,C2保持开路。同时完成另一个测量,将SR CLOCK设置改变为5而不是3,并保持所有其他设置和元件值不变,从而进一步降低压摆率。

讨论

- 加入我的myAnalog 登录 myAnalog