Altera Cyclone V GT FPGA Development Kit

详情介绍

概览

电路功能与优势

大多数分立式仪表放大器需要昂贵的匹配电阻网络才能获 得高CMR性能;然而,该电路使用一个集成式差动放大器 以及片内匹配电阻改善性能、降低成本,并最大程度减少 印刷电路板(PCB)布局面积。

图1中的复合式仪表放大器电路具有下列性能:

- 失调电压:4 mV(最大值)

- 输入偏置电流:2 pA(典型值)

- 输入共模电压:−3.5 V至+2.2 V(最大值)

- 输入差分电压:±3.5 V/G1(最大值),G1表示第一级增益

- 输出电压摆幅:0.01 V至4.75 V(典型值,150 Ω负载)

- −3 dB带宽:35 MHz(典型值,G = 5)

- 共模抑制:55 dB(典型值,10 MHz)

- 输入电压噪声:10 nV/√Hz(典型值,100 kHz RTI)

- 谐波失真:−60 dBc(10 MHz,G = 5,VOUT = 1 V p-p, RL = 1 kΩ)

大多数全集成式仪表放大器采用双极性或互补双极性工艺 制造,并针对低频应用优化,具有50 Hz或60 Hz下的高CMR 性能。然而,用于视频和RF系统中放大高速信号并提供高 频噪声信号共模抑制特性的宽带宽仪表放大器的需求正不 断增长。

需要用到极高速度、宽带宽的仪表放大器时,一种常见的 方法是使用两个高输入阻抗的分立式运算放大器来缓冲并 放大第一级的差分输入信号,然后在第二级中将单个放大 器配置为差分放大器,以便提供差分至单端转换。该配置 通常称为三运放仪表放大器。这种方法需要使用4个相对 昂贵的精密匹配电阻,以达到良好的CMR性能。如果匹配 有误差,则最终输出也会产生误差。

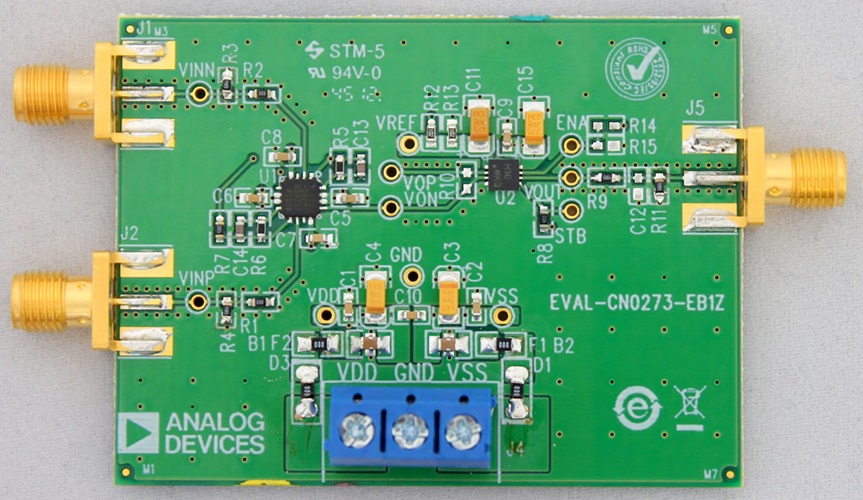

图1所示电路能够解决这一问题。该电路使用ADA4830-1 集 成式高速差动放大器。激光调整薄膜电阻以极高的精度匹 配,因此无需使用4个相对昂贵的精密匹配外部电阻。

此外,使用高速双通道ADA4817-2作为输入级放大器,允 许复合式仪表放大器提供高达80 MHz的带宽,同时电路总 增益为2.5。

采用4 mm × 4 mm LFCSP单封装的双通道ADA4817-2放大器 和集成式ADA4830-1差动放大器可极大地减少电路板空间, 从而降低大型系统的设计成本。

该电路可在噪声环境中使用,因为ADA4817-2和 ADA4830-1均提供低噪声以及高频下出色的CMR性能。

电路描述

FET放大器输入增益级

ADA4817-2(双通道)FastFET放大器是具有FET输入的单位 增益稳定、超高速电压反馈型放大器。这些放大器采用 ADI公司的专有超快速互补双极性(XFCB)工艺制造,工作 噪声极低,输入阻抗非常高且速度快,适合要求高速和高 源阻抗的应用。

ADA4817-2运算放大器配置为共享RG增益电阻。对于差分 输入,电路增益为1 + 2RF /RG。采用共模输入时,无电流流 过RG增益电阻。因此,该电路在共模输入时用作缓冲器。随后,第二级差动放大器可有效移除共模输入。

ADA4817-2的单位增益带宽积fu等于410 MHz。其闭环带宽 可通过下式近似计算:

f−3 dB = fU/G1

其中,G1为第一级的增益。

对于该电路而言,由于第一级闭环增益为10,因此−3 dB带 宽估算值为41 MHz。该值非常接近35 MHz的测试带宽。

PCB板上的寄生电容和容性负载可能会使第一增益级振 荡。使用低数值的反馈电阻,并使用反馈电容,可缓解这 一问题。

本电路选用了200 Ω的反馈电阻。反馈电容CF 为2 pF,具有 最佳带宽平坦度。

差动放大器和CMR

ADA4830-1是高速差动放大器,具有宽共模电压范围,兼 具高速和精密特性。它提供0.5 V/V的固定增益,−3 dB带宽 为84 MHz。通过片内激光调整电阻,10 MHz时该器件的 CMR典型值为55 dB。

CMR是仪表放大器极为重要的规格参数,主要取决于第二 级差动放大器使用的4个电阻的比率匹配,如图2所示。

通常,最差情况下的CMR由下式给出:=

其中,Kr是以小数表示的单个电阻容差。上述等式表示最 差情况下的CMR为34 dB,其中4个电阻具有相同的标称值 (1%容差)。该电路采用单芯片ADA4830-1差动放大器而非 分立式电阻,放大器片内集成激光调整薄膜电阻,因此具 有出色的CMR性能并节省PCB空间。直流时CMR是65 dB, 10 MHz时CMR是55 dB。

差分和共模电压考虑因素

若要最大化输入电压范围并简化电源要求,则电路第一级 采用±5 V电源,而第二级采用+5 V。最大差分输入范围由 ADA4817-2的输出摆幅决定。采用±5 V电源时,ADA4817-2 输出摆幅为±3.5 V。因此,允许的最大差分输入为±3.5 V/G1, 其中G1表示第一级增益。请注意,需在允许的最大差分输 入和第一级闭环增益之间作出权衡。

下一步,分析共模电压限制。ADA4817-2输入端的共模电 压必须位于−VS 至+VS − 1.8 V之间,即采用±5 V电源时范围 为−5 V至+2.2 V。采用±5 V电源时,ADA4817-2的输出摆幅 限制为±3.5 V(参考ADA4817-2数据手册)。因此,ADA4817-2 的输出摆幅将电路的负输入共模电压限制为−3.5 V,从而复 合电路允许的输入共模范围为−3.5 V至+2.2 V。

若要从该电路获得高性能,必须采用良好的布局、接地和 去耦技术。有关PCB布局详情,请参考 指南MT-031、 指南MT-101,以及"高速印刷电路板布局实用指南" 一文。另外, ADA4817-2数据手册和ADA4830-1数据手册中还提供了布 局指南。

电路性能

测试该复合电路的4个最重要参数:CMR、−3 dB带宽、折 合到输入端的噪声以及谐波失真,测试结果见图3至图6。

图3显示复合电路的CMR为−65 dB(直流),以及−55 dB (10 MHz)。图4显示增益为5时的带宽为35 MHz,输出负载为 100 Ω。图5显示100 kHz时,该复合电路折合到输入的噪声 仅为10 nV/√Hz,并且较高频率下的平带噪声为8 nV/√Hz。 图6显示10 MHz时,电路的THD为60 dBc(VOUT =1 V p-p, RL= 1 kΩ)。