振荡器 / 参考炉温度调节

详情介绍

概览

设计资源

评估硬件

产品型号带"Z"表示符合RoHS标准。评估此电路需要下列选中的电路板

- EVAL-CN0243-EB1Z ($595.00) High Dynamic Range RF Transmitter Signal Chain using Single External Frequency Reference for DAC Sample Clock and IQ Modulator LO Generation

驱动/参考代码

Software such as C code and/or FPGA code, used to communicate with component's digital interface.

优势和特点

- 基带提供零IF

- 复杂调制原理,如QAM

- 高动态范围

电路功能与优势

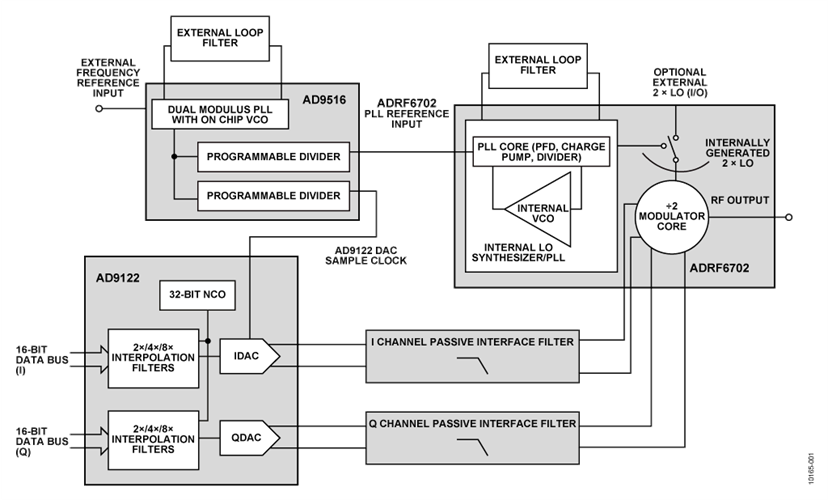

将 ADRF6702IQ调制器和 AD9122 16位双通道1.2 GSPS TxDAC结合使用可满足现代高水平QAM或OFDM无线发射器(如图1所示)的动态范围要求。该电路的动态范围出色,足以同时支持ZIF(零中频/基带)和CIF(最高200 MHz至300MHz的复合中频)。AD9122可选最高8×插值和一个32位NCO,以获得超精细中频灵敏度。

发射器的整体性能和直接组成信号链的组件动态范围息息相关。在使用DAC和IQ调制器的混合信号发射器中,这类组件的本底噪声和失真特性决定了信号链的整体动态范围。但是,DAC的本底噪声也可能由于采样时钟抖动而变得更严重,而且IQ调制器性能取决于其本地振荡器(LO)的噪声和杂散特性。因此采样时钟和LO发生采用高性能组件是高性能发射器的关键所在。

此外,在PCB板上尽量靠近DAC和调制器的位置产生这些信号并使用一个外部参考源也可大大简化设计。单独产生采用时钟和LO(LO绝大多数为数GHz信号)并且与DAC和IQ调制器保持一定距离,要求十分谨慎地处理PCB布局。哪怕最细微的布局错误都可能会引起这些关键信号发生耦合,并降低整体信号链性能。

信号链性能也很大程度上取决于DAC/ IQ调制器接口滤波器。为优化性能,建议在仔细分析所需系统规格后再设计这款无源滤波器。

ADRF6702包括一个板载分数PLL用于LO生成,这样只需一个低频参考(一般低于100 MHz)即可合成IQ调制器LO。在AD9516时钟发生器内使用PLL允许一个参考同时为ADRF6702产生DAC采样时钟和PLL参考。

图1中的电路使用AD9516-0构建而成,也可选用AD9516系列的其他产品,具体取决于所需的内部VCO频率。

图1. AD9122、ADRF6702和AD9516用于高动态范围发射器

电路描述

ADRF6702 IQ调制器是一种具有多种特性的独特器件。除出色的动态范围外,它还包括一个分数-N PLL,允许编程设置低于25 kHz的离散LO频率步进,同时仍保持足够小的整体频率倍增以避免从参考到合成器输出的相位噪声激增。

ADRF6702的另一特点是IQ调制器的2分频架构。传统IQ调制器接受1倍所需LO的LO输入频率。在内部,分布式RC网络从单LO频率输入产生所需的同相和正交LO信号。因为这属于无源RC网络,所以实现正交调制精度的带宽有限。而且,为获得出色的正交精度,外部LQ应保持频谱纯净。这种传统LO调制器架构在LO上所产生的谐波可能会降低整体调制精度。为此,当使用PLL合成器来产生IQ调制器所需的LO信号时,往往需要在IQ调制器LO输入端配置一个窄过渡带的带通或低通滤波器。

在ADRF6702的2分频LO架构中,内部使用一个简单数字分频器在较宽频带上产生近乎完美的正交。PLL合成器内部产生2倍LO,所以不必在PCB周围分配,并且因为2倍LO架构只受LO信号沿而非频率成分影响,故在合成器和IQ调制器LO之间无需配置任何滤波器。有关LO谐波对1× IQ调制器和LO滤波器设计影响的详情,请参见 电路笔记CN-0134。

图 2. DAC输出频谱,蓝色实线表示基带信号和图像,红色虚线表示DAC正弦函数

信号采样至RF、总本底杂散

基带信号通过数个步进一直到达RF发射频率。该信号在离散(采样)域开始并由DAC合成至模拟域。这一步导致DAC产生图像和失真积。如图2所示,没有失真的理想DAC将会产生多幅基带信号图像,随后必须在调制前加以滤波。使用诸如AD9122系列的插值滤波器可以抑制大多数图像能量,但仍需要在DAC和调制器之间配置一个模拟接口滤波器。不过需要权衡取舍DAC插值和模拟滤波器的阶数。DAC插值速率越高,所需的模拟滤波器阶数越低,反之亦然。作为示例,图3显示了使用4倍插值时的DAC输出频率波形。

图3.使用4倍插值的DAC输出频谱,蓝色细线表示DAC插值转移函数

多种RF杂散分量并存

由于调制积、失真积和LO频率的整数倍,该信号链可能会大幅增加杂散分量。如果我们考虑所有讨论过的潜在杂散根源,杂散成分包括:

(j × LO_freq) + (k × DAC_sample_rate) +

(l × DAC_NCO_freq) + (m × DAC_input_IF)

其中j、k、I和m均为正无穷大和负无穷大之间的整数。

DAC/调制器无源接口滤波器

在DAC和IQ调制器之间的模拟接口是缩减整体杂散频谱的关键。在DAC和IQ调制器之间的接口滤波器设计必须考虑多方面性能。

- 滤波器拓扑、阶次和3 dB截止频率

- 直流时,DAC的负载阻抗等于与IQ调制器输入阻抗并联的DAC端接电阻(一般为100 Ω差分阻抗)。IQ调制器阻抗往往>1kΩ,所以通常在IQ调制器输入端接一个分流电阻,以产生一个类似于源阻抗的负载阻抗。滤波器源阻抗和负载阻抗不相等以及信号走线寄生电容可能会在滤波器通带中产生不必要的纹波。

- PCB布局。如图4所示,ADRF6702 IQ 调制器上的I和Q基带输入位于器件的相对沿。注意在虚线圆圈内的滤波器布局。为了将DAC输出信号路由至这些引脚,走线必须向上再向下折回到ADRF6702.上的基带引脚。这些差分信号走线长度应相等,并且任何转向均应采用45°角。如果不遵守上述建议,滤波器响应中的带内波纹、相位或幅度响应可能会降低。注意,利用这个滤波器拓扑,可以差分形式使用这些电容(跨信号路径),或者也可在信号路径与接地焊盘间放置滤波器电容,以共模连接方式使用。在一些条件下(本文稍后讨论),共模电容比差分模式电容性能更佳。

- 为了获得最佳滤波器性能,这些走线应该为100 Ω差分或每条线50 Ω。注意,利用典型FR4材料,T/W比为2:1时需要一条50 Ω的走线。如果需要更高阻抗的走线,应明白走线阻抗是T/W的非线性函数(T=电路层厚度,W=走线宽度)。线越细,阻抗越高。在典型FR4层厚时,100 Ω线可以变得超细,通常接近最低设计限制。上述问题的一个解决办法是取消走线底下的接地层,并在PCB板的第三层上放上另一个接地层。这可以有效加倍T并允许使用更宽的走线。

图4. 发射器、DAC/调制器接口滤波器部分的PCB布局

DAC_MOD接口滤波器拓扑

图5所示为一种典型拓扑,它针对100 Ω差分输入和输出阻抗产生5阶最平坦的巴特沃兹响应。实际响应如图6所示。该滤波器在源阻抗和负载处使用4.6 pF电容。

这个数量级的电容(<20 pF)代表具有高截止频率的滤波器。在使用这类较小电容值时寄生电容可能对频率响应有显著影响。

图5. DAC/调制器接口滤波器拓扑、5阶巴特沃兹、3 dB BW = 220 MHz、100 Ω差分输入输出阻抗

图6. 图5所示滤波器拓扑的频率响应

DAC和失真相关杂散分量

本来使用DAC插值滤波器就可以减少调制器输入端的杂散成分,因此也可以降低RF输出端的杂散成分。但是,仍可能会存在明显的杂散成分。图7显示在下列条件下IQ调制器的RF输出频谱。

FLO = 1940 MHz

DAC 输入数据速率 = 300 MSPS

DAC 插值 = 4×

DAC 频率 = 150 MHz

DAC 输入IF频率 = 8 MHz

注意,最强的杂散分量(不含2098 MHz基频)为2400 MHz DAC时钟分量的2倍。这可能由于DAC输出的共模和差模分量包含某些来自DAC时钟的频谱。IQ调制器输入的共模抑制可消除大部分此类信号,但它仍包含大量能量。接下来的2062 MHz 和2242 MHz两个最高杂散也似乎和DAC时钟杂散相关。2242 MHz的杂散可以轻松表示成2 × (DAC时钟– DAC基频 ) = 2400 − 158。2062 MHz的杂散没有这么明显,但差不多是(3 × LO) − (3 × DAC clock) − 158 = 5820 − 3600 − 158。如果上述分析无误,并且可以在IQ调制器输入端抑制DAC时钟的共模分量,那么应该能够大幅降低杂散。

图7. IQ调制器RF输出,缺少DAC/IQ调制器滤波器,LO = 1940 MHz,DAC输入中频 = 8 MHz,DAC NCO = 150 MHz, RF = 2098 MHz

如图8所示,应用差分巴特沃兹滤波器可以大幅降低杂散水平。最强的杂散仍位于2062 MHz、2242 MHz,而2× DAC时钟杂散则位于2400 MHz处。所有三种杂散分量均已大幅降低。

图8. 使用5阶巴特沃兹滤波器、差分电容的RF频谱

改变接口滤波器的拓扑通常可以提高DAC/IQ调制器接口的共模抑制性能。在图9中,从滤波器输入两侧和滤波器输出两侧到接地,共模电容(9.0 pF)取代了输入和输出4.7 pF电容。这不会改变整体差分滤波器模式响应,但会影响此板的RF整体杂散成分。在2062 MHz和2242 MHz处的上述谐波降低至数dB,同时2× DAC时钟分量约降低15dB,接近本底噪声。

此处所示的拓扑和结果可能因布局而异,所以设计人员最好先进行滤波器布局实验,特别要注意混用差模和共模电容可以实现最低的整体本底杂散。

图9. 使用5阶巴特沃兹滤波器、在DAC调制器滤波器中组合使用差模和共模电容的RF频谱

合成器路径和PLL相位噪声

如图1所示,此电路使用一个外部参考,为ADRF6702的PLL产生AD9122 DAC采样时钟和参考时钟。AD9516是确保灵活性的关键。AD9516内置一个PLL和集成VCO。它还包含若干输出,支持差分LVPECL、LVDS或单端CMOS编程,且每个输出路径均具有独立的分频器设置。在该电路中,其中一个输出路径用于DAC时钟,而另一路输出则用于ADRF6702分数-N PLL的参考输入。

在ADRF6702中使用分数PLL有两个好处。第一,分数PLL允许超精细地调谐输出LO。例如,在输入频率为38.4 MHz、ADRF6702编程MOD值为1536时,LO可按25 kHz增量编程设置。第二,参考频率不必等于LO频率/分频比,而且还可以高很多,使分频比降低。因为输出相位噪声和参考相位杂散乘以分频比成函数关系,这意味着RF下本身具有低相位噪声。

合成器系统的一大关键指标是个别PLL和分频器所叠加的相位噪声量。图10所示为频谱分析仪在进行测量时的本底噪声(绿线)、参考发生器相位噪声(红线)以及RF频率为1961 MHz,LO为1940 MHz时的输出相位噪声(黄线)。在AD9516和ADRF6702中使用PLL组合确实可以明显产生更高的近载波相位噪声(偏移载波低于500 kHz),但不会明显增加系统的宽带噪声。AD9516和ADRF6702内VCO的环路滤波器在测量电路内均设为约100 kHz带宽。可通过降低这些环路滤波器的带宽来减少近载波相位噪声。请仔细查阅系统规格,再决定给定系统可忍受的近载波相位噪声。

图10. 频谱分析仪本底噪声、参考相位噪声和RF输出相位噪声

电路评估与测试

EVAL-CN0243-EB1Z评估板需要下列信号生成和基本测量设备和软件。

设备要求

- 5 V电源

- 低相位噪声参考信号源(10 MHz至200 MHz范围 @ +3 dBm),Rohde & Schwarz SMA100,低噪声选项或相当选项。

- ADI公司DPG2数字模式发生器

- 高动态范围频谱分析仪,Agilent E4440A或同类产品

- ADI EVAL-ADF4XXX USB适配器

- DPG2软件(DPG附带)

- ADRF6702软件,可访问 www.analog.com/ADRF6702下载

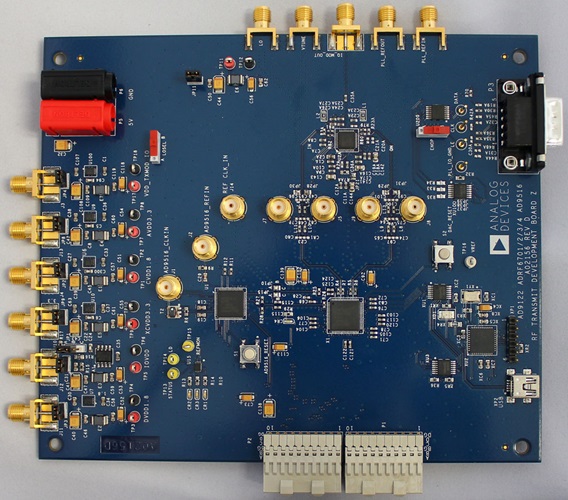

图11. EVAL-CN0243-EB1Z评估板

图12. 参考测试设置

设置与测试

请遵守下列操作步骤以正确运行EVAL-CN0243-EB1Z评估板。

- 在上电前,连接所有仪器、USB适配器和电缆,如图13所示。

- 仅需要提供一个5V电源。该电源应接到EVAL-CN0243-EB1Z评估板的香蕉插座(female banana plug)。确保电源正确连接,然后接通+5 V电源。此时总电流应显示为850 mA至900 mA。

- DPG2软件内含一个用于AD9122编程的GUI。通过编程设置AD9122的正确插值速率和NCO(视需要)。

- DPG2软件自动开启。如果所有电缆和软件工作正常,则软件应能识别DAC输入数据速率,并显示DPG界面的右下角。注意,此数据速率应等于图13中的DAC采样速率(614.4 MSPS)除以AD9122的编程插值速率。

- 注意,在激活并编程各种器件时,电流随之上升。在这步操作结束后,根据DAC采样速率,电流应介于1.4A和1.5A之间。

- 使用DPG2软件创建一个波形(提供单音、多音或通信标准信号)。开始时应使用−8 dB的数字延时来优化DAC/ADRF6702组合的线性度。还应在DPG2界面内选择复数信号生成。在波形创建完毕后,使用界面内的“加载”和“播放”按钮将数字模式载入DPG内存中。

- 启动ADRF6702图形界面。开始时,在ADRF6702图形界面中唯一需要选择的是输入参考频率和LO输出频率。要编程设置这些值,请在ADRF6702界面顶部中心点击参考输入频率或LO输出值。将会出现另一个窗口,供您输入上述值。切记:输入值后,用户必须回车返回,确保值输入界面内。

- ADRF6702编程是设置EVAL-CN0243-EB1Z评估板的最后一步。例如,如果DPG2产生一系列信号音(20 MHz至25 MHz,1MHz间隔)@ −8 dB延时,且ADRF6702的LO编程设定为1940 MHz,则频谱形状应类似于图14所示。

图13. 测试设置功能框图

图14. ADRF6702 RF输出端LO频率为1940 MHz,所需边带失调为+20 MHz,干扰边带失调为−20 MHz时的复数多音信号频谱

讨论

样片申请及购买

样片

| 产品 |

描述 |

可提供样片的 |

| AD9516-3 | 14路输出时钟发生器,集成2.0 GHz VCO | AD9516-3BCPZ |

| AD9516-0 | 14路输出时钟发生器,集成2.8 GHz VCO | AD9516-0BCPZ |

| AD9516-1 | 14路输出时钟发生器,集成2.5 GHz VCO | AD9516-1BCPZ |

| AD9122 | 双通道、16位、1200 MSPS、TxDAC+®数模转换器 | |

| ADRF6702 | 1200MHz至2400 MHz正交调制器,采用1550MHz至2150 MHz小数N分频PLL和集成式VCO | ADRF6702ACPZ-R7 |

| AD9516-2 | 14路输出时钟发生器,集成2.2 GHz VCO | AD9516-2BCPZ |

| AD9516-4 | 14路输出时钟发生器,集成1.6 GHz VCO | AD9516-4BCPZ |

- 加入我的myAnalog 登录 myAnalog