并联电流源用于提供较高的 300mA 电流输出

详情介绍

概览

设计资源

评估硬件

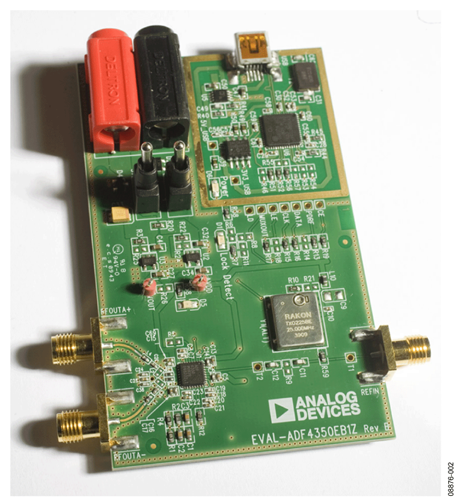

产品型号带"Z"表示符合RoHS标准。评估此电路需要下列选中的电路板

- EVAL-ADF4350EB1Z ($175.00) ADF4350 evaluation board used to evaluate this circuit. Please see "Circuit Evaluation & Test" section for set up information.

驱动/参考代码

Software such as C code and/or FPGA code, used to communicate with component's digital interface.

优势和特点

- 工作频率范围:140 MHz至4.4 GHz

- 超低噪声调节器可实现最佳系统相位噪声性能

电路功能与优势

图1所示电路使用完全集成的小数N分频PLL和VCO ADF4350,它可产生137.5 MHz至4400 MHz范围内的频率。ADF4350采用超低噪声3.3 V ADP150调节器供电,以实现最佳LO相位噪声性能。

ADP150 LDO的积分均方根噪声较低,仅为9 μV(10 Hz至100 kHz),有助于尽可能降低VCO相位噪声并减少VCO推压的影响(等效于电源抑制)。

图2是评估板的照片,它利用ADP150 LDO为ADF4350供电。ADP150代表业界噪声最低、封装最小、成本最低的LDO,采用4引脚、0.8 mm x 0.8 mm、0.4 mm间距WLCSP封装或方便的5引脚TSOT封装。因此,在设计中加入ADP150对系统成本和电路板面积的影响极小,但却能显著改善相位噪声性能。

电路描述

VCO推压的测量方法是将一个稳定的直流调谐电压施加于ADF4350 VTUNE引脚,然后改变电源电压,测量频率变化。推压系数(P)等于频率变化量除以电压变化量,如表1所示。

表1:ADF4350 VCO推压

| VCO 频率(MHz) | VTune (V) | VCO 推压(MHz/V) |

| 2200 | 2.5 | 0.73 |

| 3300 | 2.5 |

1.79 |

| 4400 | 2.5 |

5.99 |

在PLL系统中,如果VCO推压较高,则意味着电源噪声会降低VCO的相位噪声性能;如果VCO推压较低,则电源噪声不会显著降低相位噪声性能。然而,对于高VCO推压,高噪声电源会对相位噪声性能产生较大的影响。

实验显示,推压在4.4 GHz VCO输出频率时达到最大,因此我们比较了在该频率时采用不同调节器的VCO性能。ADF4350的A版评估板使用 ADP3334LDO调节器。此调节器的积分均方根噪声为27 μV(从10 Hz积分到100 kHz)。相比之下,EVAL-ADF4350EB1Z B版所用的ADP150只有9 μV。为了测量电源噪声的影响,借助一个窄PLL环路带宽(10 kHz)对VCO相位噪声进行更深入的探究。图3为该设置的示意图。

欲了解关于输出噪声密度与频率关系的更详细分析,请参考ADP3334和ADP150的数据手册。

图4显示,ADP3334调节器的噪声谱密度在100 kHz偏移时为25 nV/√Hz。ADP150则为100 nV/√Hz(图5)。

其中,L (LDO)是在频率偏移 fm时调节器对VCO相位噪声的噪声贡献(dBc/Hz);P为VCO推压系数(Hz/V); Sfm为给定频率偏移下的噪声谱密度(V/√Hz); fm为测量噪声谱密度所对应的频率偏移(Hz)。

然后,电源的噪声贡献与VCO的噪声贡献(其本身利用极低噪声电源进行测量)以RSS方式求和,得出采用给定调节器时VCO输出端的总噪声。

这些噪声以RSS方式求和,得出期望的VCO相位噪声:

本例选择100 kHz的噪声谱密度偏移,并使用6 MHz/V的推压系数,带理想电源的VCO噪声取值−110 dBc/Hz。

表2. VCO噪声的计算和测量

| ADP3334 | ADP150 | |

| 调节器的噪声贡献 (nV/√Hz) |

150 | 25 |

| 调节器的噪声贡献 (dBc/Hz) |

-104 | -119.5 |

| VCO输出端的总计算噪声 (dBc/Hz) |

-103 | -109.5 |

| 100 kHz偏移时VCO噪声测量结果 (dBc/Hz) |

-102.6 | -108.5 |

The integrated phase noise improves from 1.95° to 1.4° rms also. The measured results correlate very closely with the calculations and clearly show the benefit of using the ADP150 with the ADF4350.

A complete design support package for this circuit note can be found at http://www.analog.com/CN0147-DesignSupport.

常见变化

电路评估与测试

Equipment Needed

Windows® XP, Windows, Vista (32-bit), or Windows 7 (32-bit) PC with USB Port, the ADF4350EB1Z, the ADF4350 programming software, 5.5 V power supply, and a spectrum analyzer such as a Rhode and Schwartz FSUP26. See this circuit note CN-0147 and UG-109 user guide for evaluation board EVAL-ADF435EB1Z and the ADF4350 data sheet.

Getting Started

This circuit note, CN-0147, contains a description of the circuit, the schematic, and a block diagram of the test setup. The ser guide, UG-109, details the installation and use of the EVAL-ADF4350 evaluation software. UG-109 also contains board setup instructions and the board schematic, layout, and bill of materials.

Functional Block Diagram

This circuit note, CN-0147, contains the function block diagram of the described test setup in Figure 3.

Setup and Test

After setting up the equipment, standard RF test methods should be used to measure the spectral purity of the output signal.

讨论

样片申请及购买

样片

| 产品 |

描述 |

可提供样片的 |

| ADF4350 | 集成VCO的宽带频率合成器 | ADF4350BCPZ |

| ADP150 | 超低噪声、150 mA CMOS线性调节器 | ADP150ACBZ-1.8-R7 ADP150ACBZ-2.5-R7 ADP150ACBZ-2.6-R7 ADP150ACBZ-2.75R7 ADP150ACBZ-2.8-R7 ADP150ACBZ-2.85R7 ADP150ACBZ-3.0-R7 ADP150ACBZ-3.3-R7 ADP150AUJZ-1.8-R7 ADP150AUJZ-2.0-R7 ADP150AUJZ-2.5-R7 ADP150AUJZ-2.65-R7 ADP150AUJZ-2.8-R7 ADP150AUJZ-3.0-R7 ADP150AUJZ-3.3-R7 |

- 加入我的myAnalog 登录 myAnalog