LTM4601HV 5V/8A 设计无差分放大器

详情介绍

概览

设计资源

评估硬件

产品型号带"Z"表示符合RoHS标准。评估此电路需要下列选中的电路板

- AD9434-500EBZ ($250.00) AD9434 evaluation board used to evaluate this circuit. Please see "Circuit Evaluation & Test" section for connection information.

驱动/参考代码

Software such as C code and/or FPGA code, used to communicate with component's digital interface.

优势和特点

- 12位、500MSPS宽带接收器

- 抗混叠滤波器

- 低失真差分驱动器

- 输入为140MHz时,SNR为64dB

- 输入为140MHz时,SFDR为70dB

电路描述

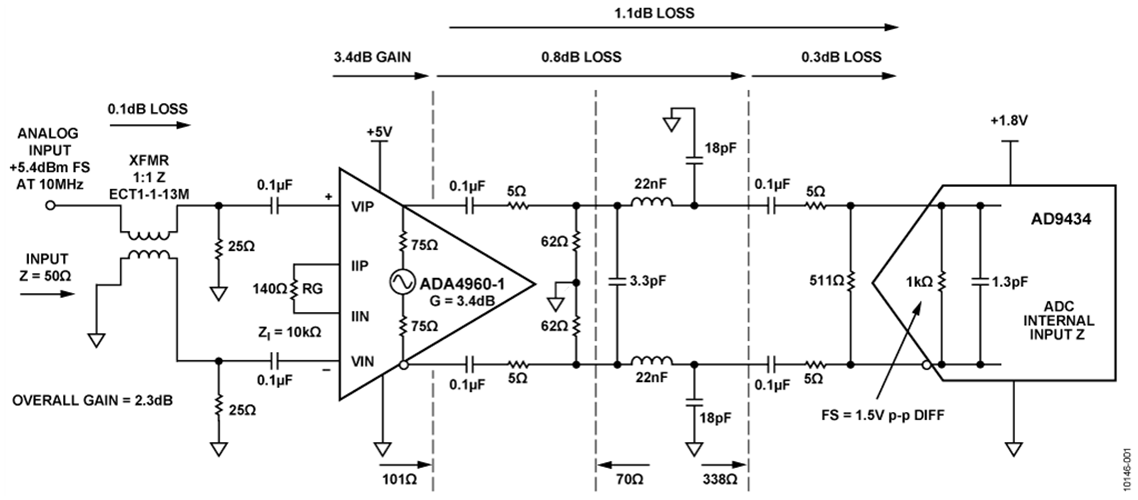

该电路接受单端输入并使用宽带宽(3 GHz) M/A-COM ECT1- 1-13M 1:1变压器将其转换为差分信号。5 GHzADA4960-1差分放大器的差分输入阻抗为10 kΩ。通过选择外部增益设置电阻RG,增益可在0 dB至18 dB范围内调整。差分输出阻抗为150 Ω。

ADA4960-1是AD9434的理想驱动器,通过低通滤波器可在ADC中实现全差分架构,提供良好的高频共模抑制,同时将二阶失真产物降至最低。ADA4960-1根据外部增益电阻提供0 dB至18 dB的增益。此电路中,使用3.4 dB增益补偿滤波器网络(1.1 dB)和变压器(0.1 dB)的插入损耗,从而提供2.3 dB的总信号增益。约5.4 dBm的输入信号在ADC输入端产生满量程1.5 V p-p差分信号。

抗混叠滤波器是采用标准滤波器设计程序设计出的三阶巴特沃兹滤波器。选择巴特沃兹滤波器是因为它在通带内具有平坦响应。三阶滤波器产生1.05的交流噪声带宽比,可借助多种免费滤波器程序进行设计,例如Nuhertz Technologies Filter Free (hwww.nuhertz/filter)或Quite Universal Circuit Simulator (Qucs) Free Simulation (www.qucs.sourceforge.net)。

为了实现最佳性能,ADA4960-1应载入100 Ω的净差分负载。5 Ω串联电阻将滤波器电容与放大器输出隔离开,62 Ω电阻与下游阻抗并联,当加入10 Ω串联电阻时可产生101 Ω的净负载阻抗。

5 Ω电阻与ADC输入串联,将内部开关瞬变与滤波器和放大器隔离开。511 Ω电阻与ADC并联,用于降低ADC的输入阻抗,使性能更具可预测性。

三阶巴特沃兹滤波器采用70 Ω的源阻抗、338 Ω的负载阻抗和360 MHz的3 dB带宽设计而成。程序计算出的值如图2所示。

图2. 三阶差分巴特沃兹滤波器设计,ZS = 70 Ω,ZL = 338 Ω,FC = 360 MHz

为滤波器无源元件选择的值是最接近程序生成值的标准值。

将ADC的内部1.3 pF电容从第二分流电容值(10.01 pF)减去,获得值8.71 pF。本电路中,该电容使用两个18 pF接地电容来实现,如图1所示。这样既能提供相同的滤波效应,又能得到一定的交流共模抑制。

表1总结了系统的测量性能,其中3 dB带宽为290 MHz。网络的总插入损耗约为1.1 dB。图3所示为带宽响应;图4所示为SNR和SFDR性能。

| Performance Specs @ 1.5V p-p Fs |

Final Results |

| Cutoff Frequency (-3 db) |

290 MHz |

| Pass-Band Flatness (6MHz to 200MHz) |

1 dB |

| SNRFS @ 140MHz |

64.1 dBFS |

| SFDR @ 140MHz |

70.4 dBc |

| H2/H3 @ 140MHz |

85.0 dBc/70.4 dBc |

| Overall Gain @ 10MHz |

2.3 dB |

| Input Drive @ 10MHz |

5.4 dBm |

图3. 通带平坦度性能与频率的关系

图4. SNR/SFDR性能与频率的关系

滤波器和接口设计程序

为实现最佳性能(带宽、SNR、SFDR等),放大器和ADC应对一般电路形成一定设计限制:

- 放大器应参考数据手册推荐的正确直流负载,以获得最佳性能。

- 放大器与滤波器的负载间必须使用正确数量的串联电阻。这是为了防止通带内的不需要的峰值。

- ADC的输入应通过外部并联电阻降低,并使用正确串联电阻将ADC与滤波器隔离开。此串联电阻也会减少峰值。

图5所示的一般电路适用于大多数高速差分放大器/ADC接口,将作为本文的讨论基础。此设计方法倾向于利用大多数高速ADC的相对较高输入阻抗和驱动源(放大器)的相对较低阻抗,将滤波器的插入损耗降至最低。

图5. 采用低通滤波器的一般差分放大器/ADC接口

基本设计流程如下:

- 选择外部ADC端接电阻RTADC,使得RTADC与RADC的并联组合介于200 Ω和400 Ω之间

- 根据经验和/或ADC数据手册建议选择RKB,通常介于5 Ω和36 Ω之间。

- 使用下式计算滤波器负载阻抗:

ZAAFL = RTADC || (RADC + 2RKB)

- S选择放大器外部串联电阻RA。如果放大器差分输出阻抗在100 Ω至200 Ω范围内,RA应小于10 Ω。如果放大器输出阻抗为12 Ω或更低,RA应介于5 Ω和36 Ω之间。

- 选择RTAMP,使放大器获得的总负载ZAL最适合通过以下公式选择的特定差分放大器:

ZAL = 2RA + (ZAAFL || 2RTAMP)

- 计算滤波器源阻抗

ZAAFS = 2RTAMP || (ZO + 2RA)

- 使用滤波器设计程序或表,利用源阻抗、负载阻抗、ZAAFS和ZAAFL、滤波器类型、带宽、阶次等设计滤波器。带宽比采样速率的一半高出约40%,以确保直流至fs/2频率范围内的平坦度。

- 内部ADC电容CADC应从程序生成的最终分流电容值减去。程序将给出差分分流电容值CSHUNT2。最终共模分流电容为:

经过上述初步计算,应了解电路的下列项目。

- CAAF2值应至少为10 pF,比CADC大数倍。这样可将滤波器对CADC波动的敏感度降至最低。

- ZAAFL与ZAAFS之比不应高于约7,使滤波器在大多数滤波器表和设计程序的限值内

- CAAF1值应至少为5 pF,以尽可能降低对寄生电容和元件波动的敏感度。

- 电感LAAF应为合理值,至少为数nH。

在某些情况下,滤波器设计程序可提供一个以上独特解决方案,特别是对于更高阶滤波器。应始终选择采用最合理元件值组合的解决方案。另外应选择结束于分流电容的配置,以便分流电容与ADC输入电容组合。

电路优化技术和权衡

本接口电路内的参数具有高互动性;因此优化电路的所有关键规格(带宽、带宽平坦度、SNR、SFDR、增益等)几乎不可能。不过,通过变更RA和RKB,可以最大程度地减少通常发生于带宽响应内的尖峰。

通带内的尖峰随输出串联电阻RA值增加而降低。然而,此电阻值增加时,信号衰减也会增加,放大器必须驱动更大信号才能填充ADC的满量程输入范围。

RA值也会影响SNR性能。更大值在降低带宽峰化的同时倾向略微提高SNR,因为驱动ADC满量程需要更高信号电平。

ADC输入端的RKB串联电阻应选择为尽量减少任何残余电荷注入(从ADC内部采样电容)造成的失真。增加此电阻也倾向减小带内尖峰。

不过,增加RKB会增加信号衰减,因此放大器必须驱动更大信号才能填充ADC的输入范围。

优化通带平坦度的另一方法是略微变更滤波器分流电容CAAF2。

ADC输入端接电阻RTADC通常应选择为使净ADC输入阻抗介于200 Ω和400 Ω之间。降低该电阻可减少ADC输入电容的效应并稳定滤波器设计,但会增加电路的插入损耗。提高该值也会减小峰值。

上述因素的权衡可能有些困难。本设计中,每个参数权重相等;因此所选值代表了所有设计特征的接口性能。某些设计中,可根据系统要求选择不同值,以优化SFDR、SNR或输入驱动电平。

请注意,本设计中的信号与0.1 μF电容进行交流耦合,以阻挡放大器、其端接电阻和ADC输入之间的共模电压。共模电压的详情请参见AD9434数据手册。

无源元件和PCB寄生考虑因素

该电路或任何高速电路的性能都高度依赖于适当的PCB布局,包括但不限于电源旁路、受控阻抗线路(如需要)、元件布局、信号布线以及电源层和接地层。高速ADC和放大器PCB布局的详情请参见教程MT-031和 教程MT-101。

低寄生表面贴装电容、电感和电阻应用于滤波器内的无源元件。所选电感来自Coilcraft 0603CS系列。滤波器所用表面贴装电容的稳定性和精度是5%、C0G、0402型。

系统的完整文档请参见CN-0238设计支持包(www.analog.com/ CN0238-DesignSupport)。

常见变化

对于需要更少带宽、更高杂散性能和更低功耗的应用,可使用ADA4927-1/ ADA4927-2或 ADA4938-1/ ADA4938-2。ADA4927-1带宽为2.3 GHz,仅使用20 mA的电流,而ADA4938-1带宽为1.0 GHz,使用37 mA的电流。

对于需要更低分辨率的应用,8位、500 MSPS AD9484与AD9434引脚兼容。AD9484在250 MHz模拟输入频率下的SNR为47 dBFS。

对于需要更低采样速率的应用,12位、170 MSPS/210 MSPS/250 MSPSAD9230是与AD9434引脚兼容的ADC,且具有大致相同的动态性能。

对于需要数字预失真(DPD)观测的应用,也可考虑12位、500 MSPSAD6641该产品具有片内16k × 12位FIFO。

电路评估与测试

此电路使用经过修改的AD9434-500EBZ电路板和HSC-ADC-EVALCZFPGA数据采集板。这两片板具有对接高速连接器,可以快速完成设置并评估电路性能。经过修改的AD9434-500EBZ板包含依照本笔记所述进行评估的电路,HSC-ADC-EVALCZ数据采集板配合Visual Analog评估软件和SPI控制器软件使用,以正确控制ADC并采集数据。AD9434-500EBZ板的原理图、BOM和布局请参见用户指南UG-290。CN-0238设计支持包中的“readme.txt”文件(www.analog.com/CN0238-DesignSupport)说明了对标准AD9434-500EBZ板做出的修改。应用笔记AN-835详细说明了如何设置硬件和软件,以运行本电路笔记所述的测试。