LTC3630A 4V~63V 输入至 –12V 输出的正至负转换器

详情介绍

概览

设计资源

评估硬件

产品型号带"Z"表示符合RoHS标准。评估此电路需要下列选中的电路板

- ADL5801-EVALZ ($140.00) High IP3, 10 MHz to 6 GHz, Active Mixer

- EVAL-ADF4351EB1Z ($175.00) Wideband Synthesizer with Integrated VCO

驱动/参考代码

Software such as C code and/or FPGA code, used to communicate with component's digital interface.

优势和特点

- 6GHz有源混频器

- 无缝LO接口

- 小尺寸

电路功能与优势

电路描述

ADF4351是一款宽带小数N分频和整数N分频锁相环PLL频率合成器,覆盖从35 MHz至4400 MHz的频率范围。该器件具有一个集成电压控制振荡器(VCO),其基波频率范围为2200 MHz至4400 MHz。利用一组分频器可实现多倍频程操作。

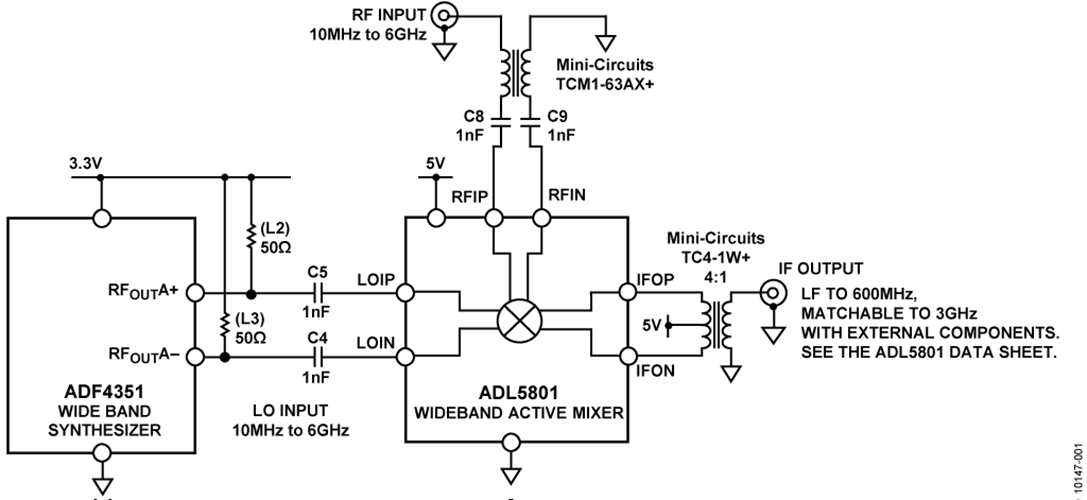

ADL5801是一款高线性度、双平衡、有源混频器,集成一个LO缓冲器放大器,所支持的频率范围为10 MHz至6000 MHz。该混频器有一种偏置调节功能,可优化输入线性度、噪声系数和直流工作电流。图1所示电路有一个简单的LO接口,适用于需要宽带上变频或下变频的应用。接口覆盖的RF频率范围为35 MHz至4400 MHz。

ADF4351 PLL有一个差分LO输出接口,ADL5801针对差分LO驱动而优化。差分接口提供共模噪声抑制和偶数阶谐波消除功能。

正常情况下,建议在ADF4351的输出端口使用上拉偏置电感。该解决方案可输出更高的功率,但会限制器件的频率范围。标准评估板配有两个7.5 nH上拉电感,在500 MHz以上频率可发挥出最佳性能。在图1所示电路中,偏置电感被两个50 Ω的上拉电阻取代,以降低输出接口对频率的依赖性。这一变化导致输出功率下降;然而,ADL5801可以容忍这一限制,因为该器件的额定LO驱动电平低至−10 dBm。图2比较了器件在阻性和感性两种上拉网络条件下的输出功率。

阻性上拉网络代表着输出端100 Ω的额定差分阻抗,而ADL5801LO端口的差分输入阻抗为50 Ω。混频器LO路径中阻抗的不匹配并不会导致电路性能下降。然而,建议尽量缩短器件间连接走线的长度,以降低阻抗不匹配导致的影响。

以上描述的PLL混频器接口表现出优秀的宽带性能,如图3和图4所示。电路在3500 MHz以下频率可使输入IP3维持在25 dBm以上,在不超过4400 MHz的频率下则维持在23 dBm。根据电路表现,在整个工作频段内,转换增益超过−0.7 dB,噪声系数小于12.2 dB。

ADF4351会激活其分频器网络中的几个部分,以产生跨越多个倍频程的输出频率。电路的功耗取决于工作频率和混频器的偏置点。这些部分的组合决定着PLL的功耗。例如,当对PLL编程以输出35 MHz的频率时,器件会激活全部6个分频器网络,功耗为132 mA。该点代表器件的最差条件功耗点。类似地,ADL5801的偏置电平,可用来调节IP3和噪声系数,决定着混频器的功耗。VSET引脚用于调节器件的偏置电平。图5和图6所示为混频器的直流电流、输入IP3和噪声系数性能,表现为VSET电压的函数。

电路评估与测试

上述电路是利用针对ADF4351 ( EVAL-ADF4351EB1Z) 和 ADL5801 (ADL5801-EVALZ) 的标准评估板实现的。ADF4351评估板套件包括一个参考晶振、控制软件以及器件

工作所需要的编程接口电缆。控制软件提供相应的选项,用于设置输出频率、功率水平、参考频率和各种其他特性。

表1和表2列出了为实现该应用电路在评估板上改动的组件。

表1.EVAL-ADF4351EB1Z上的组件改动情况| 位置 | 默认值 | 新值 |

| L2, L3 | 7.5 nH | 50 Ω |

| L1, L4 | 1.9 nH | 0 Ω |

表2. EVAL-ADF4351EB1Z上的组件改动情况

| 位置 | 默认值 | 新值 |

| T2/T4/T7 | Mini-Circuits TCM1-1-13M+ | 0 Ω |

| C4, C5 | 100 pF | 1 nF |

图8所示为测试设置的功能框图。PLL的输出以及混频器的LO端口是用一个评估用同轴通孔连接器桥接的。图7所示为两块连接起来的评估板的照片。以下列出了用来评估电路的设备清单。

- 带USB端口的Windows® XP、Windows® Vista(32位)或Windows® 7(32位)PC

- ADF4351评估板(EVAL-ADF4351EB1Z)

- ADL5801评估板(ADL5801-EVALZ)

- RF信号发生器(Rohde & Schwarz SMT06或等效器件)

- 频谱分析仪(Rohde & Schwarz FSEA30或等效器件)

- 电源: Agilent E3631或等效产品

EVAL-ADF4351EB1Z: +5.5 V

ADL5801-EVALZ: +5 V (VPOS), +3.6V (VSET)

控制软件用来对所需LO频率和输出功率编程。图9是用于驱动ADF4351的软件配置的屏幕截图。有关ADF4351的设置详情,请参阅 UG-435用户指南、ADF4351小数-N分频PLL频率合成器评估板 以及 UG-476 用户指南、PLL 软件安装指南 。

利用一个外部电源,以3.6 V的VSET电压对ADL5801进行偏置。该外部偏置连接可以用板载连接代替,后者用一个阻性分频器网络通过电源引脚来路由。连接位置R10,使R7和R8开路,即可使能该阻性分频器网络。表3提供了实现目标混频器偏置电平所需要的R10值。有关更多信息,请参阅ADL5801数据手册中的“RF电压-电流(V-I)转换器”部分。

| R10 (Ω) | VSET (V) | IPOS (mA) |

| 226 | 4.5 | 160 |

| 562 | 4.01 | 146 |

| 568 | 4 | 145 |

| 659 | 3.9 | 142 |

| 665 | 3.89 | 142 |

| 694 | 3.85 | 142 |

| 760 | 3.8 | 139 |

| 768 | 3.79 | 139 |

| 1000 | 3.6 | 133 |

| 1100 | 3.53 | 131 |

| 1150 | 3.5 | 130 |

| 1200 | 3.47 | 129 |

| 1300 | 3.4 | 127 |

| 1400 | 3.35 | 126 |

| 1500 | 3.3 | 124 |

| 1600 | 3.26 | 122 |

| 1700 | 3.21 | 121 |

| 1800 | 3.17 | 120 |

| 1900 | 3.14 | 119 |

| 2000 | 3.1 | 118 |

| 2300 | 3 | 114 |

| 5900 | 2.5 | 98 |

| 开路 | 2.03 | 82 |

为了展示电路对35 MHz至4400 MHz范围内RF频率的支持能力,采用高边LO配置以及153 MHz的IF频率来运行该器件。