LTC7138 12V/400mA 汽车电源

详情介绍

概览

设计资源

驱动/参考代码

Software such as C code and/or FPGA code, used to communicate with component's digital interface.

优势和特点

- 13 GHz RF PLL输出

- 200 MHz跳频相位建立时间短于5 μs

电路功能与优势

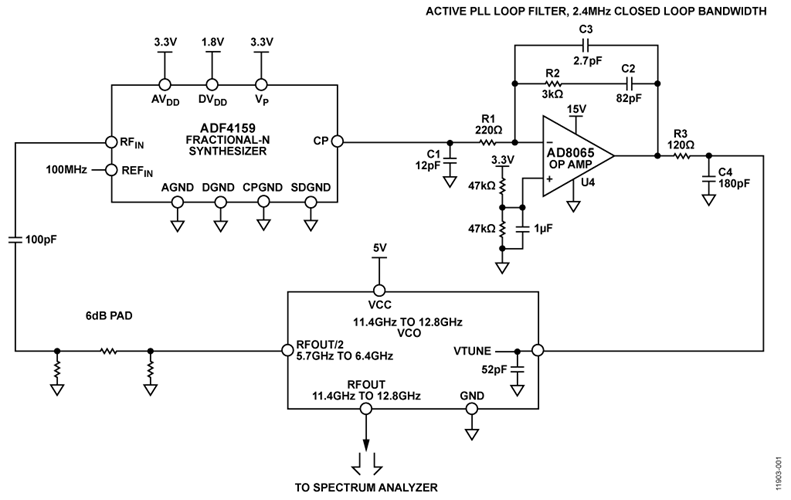

图1所示PLL电路采用13 GHz小数N分频频率合成器、宽带有源环路滤波器和VCO,5°以内的200 MHz跳频相位建立时间短于5μs。

采用带宽为2.4 MHz的有源环路滤波器获得该性能。 由于ADF4159 鉴频鉴相器(PFD)最大频率为110 MHz,并且AD8065运算放大器具有145 MHz的高增益带宽积,因此可获得该宽带宽环路滤波器性能。

有源滤波器中使用的AD8065运算放大器能够采用24 V电源电压工作,允许控制调谐电压为0 V至18 V的大多数宽带VCO。

电路描述

在PLL和VCO频率合成系统中,获得低于5μs的频率和相位建立时间需极宽的环路带宽。环路带宽(LBW)定义控制环路的速度。更宽的LBW允许更快的建立时间,但会牺牲相位噪声和杂散信号的衰减能力。

图1所示电路将ADF4159锁定至12 GHz VCO (MACOM MAOC-009269)的RFOUT/2 信号(~6 GHz)。 然而,具有 RFOUT/2 信号且 最高为24 GHz的VCO可配合ADF4159使用,因为它支持的最高RF输入为13 GHz。

ADF4159小数N分频频率合成器

在小数N分频架构PLL中,来自∑-△型调制器(SDM)的噪声在PFD频率(fPFD)的一半处达到峰值。例如,如果小数N分频PLL的PFD频率为32 MHz,则未经滤波的SDM噪声在16 MHz处达到峰值。SDM噪声使环路不稳定,导致PLL无法锁定。 图2显示此条件下的仿真相位噪声曲线。

图2. 12 GHz输出时的相位噪声曲线 (fPFD = 32 MHz , LBW = 2.4 MHz)

ADF4159的最大PFD频率为110 MHz。这表示未经滤波的SDM噪声将在55 MHz处达到峰值。图3显示PFD频率为110 MHz时的相位噪声曲线。SDM噪声出现在距离载波较大的偏移处,因此采用环路滤波器可将其滤除。

图3. 12 GHz输出时的相位噪声曲线(fPFD = 110 MHz,LBW = 2.4 MHz)

ADF4159较高的最大PFD频率同样很重要,因为建议将LBW保持在1/10 PFD频率以下,以保证稳定性。

ADF4159的最大RF输入频率为13 GHz。在该电路配置中,ADF4159实际上由VCO RFOUT/2 信号驱动。这表示当VCO主要输出12 GHz时,ADF4159实际上锁定在6 GHz。

该配置意味着可以使用24 GHz VCO,从而12 GHz的RFOUT/2 信号反馈回ADF4159。评估板的尺寸可支持各种32引脚5 mm ×5 mm LFCSP VCO。

ADF4159内部电荷泵的电源电压为3.3 V。然而,很多宽带VCO要求具有最高18 V的调谐电压。为了满足这一要求,需要使用有源环路滤波器。有源滤波器将ADF4159的输出调谐范围与运算放大器的增益相乘。更多详情,请参见本电路笔记的AD8065部分。

ADF4159支持可编程电荷泵电流特性。该特性允许用户轻松修改环路滤波器的动态特性而无需改变物理元器件。在本电路的2.5 mA电荷泵电流下,LBW设计为2.4 MHz。可以降低电荷泵电流,从而可在不对环路滤波器元件做出物理改变的情况下降低LBW。

该电路的ADIsimPLL仿真请参见CN0302设计支持包(http://www.analog.com/CN0302-DesignSupport)。

使用AD8065的有源滤波器

AD8065运算放大器电源电压范围为24 V,增益带宽积(GBP)约为145 MHz,并具有低噪声(7 nV/√Hz)特性。 该特性使其成为有源滤波器的理想选择。

对于大多数PLL应用而言,建议相位裕量采用45°至55°,以保持稳定的环路,并在最大程度上缩短建立时间。 在有源环路滤波器中(比如环路滤波器中存在运算放大器),则在运算放大器的单位增益频率(或增益带宽积)处会产生额外的极点。这一额外极点会引入更多相位滞后,因此在不同极点频率下可能会出现环路不稳定现象。

表1. 相位滞后作为GBP的函数: LBW比

| GBP/LBW 比 |

额外相位迟滞(°) |

| 5(e.g.GBW=1 MHz,LBW=200 kHz) |

11.3 |

| 10 | 5.7 |

| 20 | 2.9 |

GBP与LBW之比越高,相位迟滞越低。例如,表1显示若GBP/LBW的比值为10将使相位裕量下降5.7°。若GBP/LBW比值过低,则相位裕量同样会变得很低,使环路不稳定。

本电路采用2.4 MHz LBW,因此AD8065 145 MHz GBP的相位迟滞几乎可以忽略不计(GBP/LBW = 60)。

与OP184有源滤波器进行比较

OP184是一款有源滤波器PLL应用中常用的运算放大器。然而,OP184不适合用于极宽LBW的应用,因为其GBP为4 MHz。对相位裕量进行优化后,OP184便可用于宽LBW应用,但OP184终将限制最大LBW。

有源滤波器中的运算放大器配置为反相模式,因此ADF4159采用鉴相器的负极性编程。反相配置比较容易实现,因为运算放大器正输入能以固定电压偏置,不随运算放大器输出改变而变化,而在同相配置中运算放大器输出会改变。

AD8065 还可用作缓冲器,降低VCO的输入电容。对于2.4 MHzLBW无源滤波器,VCO输入端与滤波器最后一个电容的组合电容值必须为1.5 pF左右。但是,VCO单独测得的输入电容为52 pF。

对于环路滤波器电容,建议采用C0G/NP0陶瓷电容(比标准电容具有更快的放电时间),以最大程度缩短相位建立时间。

该电路要求具有出色的布局、接地和去耦技术,如教程MT-031 和 MT-101所述。 可在CN-0302设计支持包(www.analog.com/CN0302-DesignSupport )中找到完整的原理图、布局文件和物料清单。

测试结果

电路的测量相位噪声如图4所示。200 MHz跳频的频率和相位建立时间分别如图5和图6所示。

电路评估与测试

使用AD8065而非OP184,为实现2.4 MHz有源滤波器而需要对标准EV-ADF4159EB1Z 所做的修改如下所示:

- 以AD8065ARZ代替U4(8引脚SOIC)

- 以220Ω、1%、0603代替R1

- 以3 kΩ、1%、0603代替R2

- 以120Ω、1%、0603代替R3

- 以12 pF、10%、0603代替C1

- 以82 pF、10%、0603代替C2

- 以2.7 pF、5%、0603代替C3

- 保持C4、180 pF不变

设备要求

- 针对AD8065运算放大器和2.4 MHz LBW滤波器元件修改的EV-ADF4159EB1Z评估板

- ADF4159评估软件

- 运行Windows®的PC,带USB端口

- +15 V 电源

- +5.5 V 电源

- 频谱分析仪:R&S:FSUP26、FSQ26、FSW26、Agilent E5052B或同等设备。

测试设置功能框图

测试设置的功能框图如图7所示,该设置的照片如图8所示。有关运行测试和设置软件的详情,请参见用户指南UG-383。