LTC3638 36V~140V 至 36V/250mA 具 75mA 输入电流限制

详情介绍

电路功能与优势

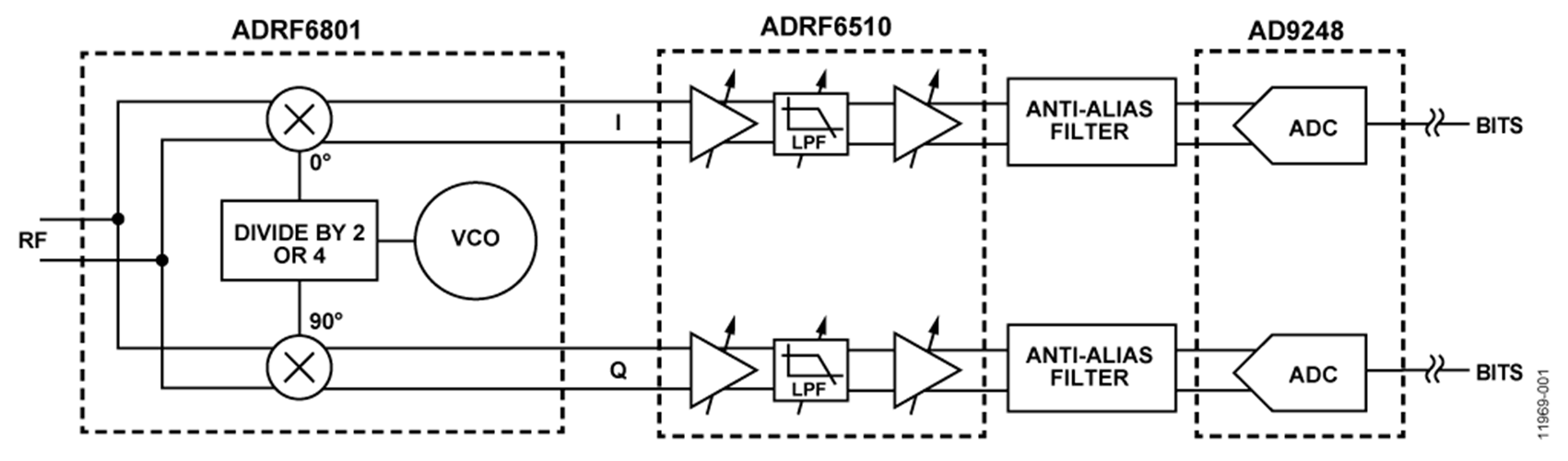

本电路是灵活的频率捷变直接变频中频至基带接收机,其5 dB固定转换增益可降低级联噪声系数。可变基带增益用来调节信号电平。基带ADC驱动器还包括可编程低通滤波器,可消除通道外阻塞和噪声。

此滤波器的带宽可随着输入信号带宽变化而动态地调节。这样可以确保由本电路驱动的ADC的可用动态范围得到充分使用。

本电路的核心部分是一个集成式IQ解调器,由小数N分频PLL和VCO组成。由于仅有一个(可变)参考频率,PLL/VCO可提供范围为750 MHz至1150 MHz的本振(LO)信号。精确的正交平衡和低输出直流失调确保了对误差矢量幅度(EVM)的影响极小。

本电路内所有元件间的接口均采用全差分式。如果不同级间需要直流耦合,相邻级的偏置电平彼此兼容。

电路描述

本电路笔记中描述了接收机的直接变频(也称为零差或零中频)架构。与可以执行多次频率转换的超外差式接收机相比,直接变频无线电只能执行一次频率转换。一次频率转换的优势如下:

- 降低接收机复杂性,减少所需级数;提高性能和降低功耗

- 避免镜像抑制问题和不需要的混频产物;只需要基带上的一个LPF

- 高灵敏度(相邻通道抑制比[ACRR])

图1显示了该系统的基本原理示意图,包括由小数N分频PLL和VCO组成的集成式正交解调器,后接具有可变基带增益的可编程低通滤波器。信号链的最后一部分是一个抗混叠滤波器和一个双通道ADC。

理想情况下,第一级的输入和最后级的输出应设置系统的动态范围(信噪比)。实际上,情况可能并非如此。

IQ解调器、小数N分频PLL和VCO

输入信号施加至ADRF6801正交解调器,该解调器将频率转换为零中频。ADRF6801片内集成频率合成器,提供所需的LO信号。该频率合成器由小数N分频PLL和VCO组成,在标准闭环模式下可提供750 MHz至1150 MHz的LO频率范围。

ADRF6801使用两个双平衡混频器,一个用于I通道,一个用于Q通道。提供给混频器的LO使用2分频正交分相器生成。这为I和Q通道分别提供了0°和90°信号。ADRF6801在RF输入至基带I和Q输出之间提供约5 dB的转换增益。

低通滤波器、基带可变增益放大器(VGA)和ADC驱动器

低通滤波器、基带可变增益放大器(VGA)和ADC驱动器低通滤波器、基带增益和ADC驱动功能全部使用ADRF6510来实现。施加于ADRF6510的信号现在具有独立的I和Q路径,信号首先通过前置放大器放大,然后进行低通滤波,以抑制任何不需要的带外信号和/或噪声,最后通过VGA放大。

ADRF6510的每个通道可分为三个级

- 前置放大器

- 可编程低通滤波器

- VGA和输出驱动器

通过GNSW引脚,前置放大器具有6 dB或12 dB的用户可选增益。低通滤波器可通过SPI端口设置为1 MHz至30 MHz的转折频率,步进为1 MHz。VGA具有50 dB增益范围,增益斜率为30 mV/dB。VGA增益通过GAIN引脚控制,GNSW引脚被拉低时范围可为−5 dB至+45 dB,GNSW引脚被拉高时范围可为+1 dB至+51 dB。输出驱动器能够将1.5 V p-p差分电压驱动至1 k 负载内,同时保持高于60 dBc的HD2和HD3。

可施加于低通滤波器同时仍在ADRF6510内保持可接受的HD电平的最大连续波(CW)信号为2 V p-p,此时增益最小(GNSW = 0 V,GAIN = 0 V) 。

ADRF6510发出的IQ信号可施加于模数转换器(ADC),例如AD9248,但必须首先在两级之间部署无源低通滤波。

抗混叠滤波器

通过抗混叠滤波器的I和Q信号有助于:

- 减少带外噪声

- 减少ADRF6510的输出噪声(特别是在较高的增益下)

- 减少来自ADC的电荷反冲

- 有助于减少带外阻塞(虽然它们应当由ADRF6510的滤波功能加以消减)

抗混叠滤波器是一个低通滤波器,设计为具有约30 MHz至120 MHz的转折频率范围。如果已知信号的频谱成分低于30 MHz,那么可以选择较低的转折频率。

总共在系统中测试了5个抗混叠滤波器。前3个测试的抗混叠滤波器为差分RC型,如图2所示。滤波器1的R = 33 ,C = 18 pF。这使得低通转折频率为大约134 MHz。

滤波器2的R = 33 ,C = 39 pF,因此低通转折频率为62 MHz。最后,滤波器3的R = 33 ,C = 68 pF,因此转折频率为35.5 MHz。图3中的滤波器4是一款LC滤波器,转折频率为33 MHz;图4中的滤波器5是一款RLC滤波器,转折频率也是33 MHz。

来自抗混叠滤波器的信号施加于ADC。AD9248是一款双通道、14位、65 MSPS 3 V ADC,集成高性能采样-保持放大器和基准电压源。

测量结果: ADRF6510和ADRF6510/ADRF6801组合的EVM4 QAM

5 MSPS调制信号施加于ADRF6801正交解调器的输入端,并测量误差矢量幅度(EVM)。使用两块AD8130-EBZ评估板 将ADRF6801和ADRF6510的差分输出信号转换为单端信号。有关测试设置的更多信息,请参见“电路评估和测试”部分。

EVM衡量数字发射机或接收机的性能质量,反映幅度和相位误差所导致的实际星座点与理想位置的偏差,如图5所示。

图6显示EVM与ADRF6801输入功率的关系,仅使用ADRF6801和ADRF6801,后接ADRF6510。对于ADRF6801和ADRF6510曲线,扫描为保持1.5 V p-p输出电压作为ADRF6801输入功率所需的ADRF6510增益变化。施加于ADRF6510的前置放大器增益设为6 dB。

单独测试ADRF6801时,需注意,对于高输入信号电平,EVM在达到大约+5 dBm输入功率之前都不会下降。但当ADRF6801驱动ADRF6510时,EVM将在约0 dBm输入功率时开始下降。这是因为当前置放大器增益设为6 dB且模拟增益为最小值时,ADRF6510上的低通滤波器只能处理2 V p-p,即ADRF6510输入引脚为1 V p-p。超出此信号电平会导致失真,使EVM下降。

对于低输入信号电平而言,SNR变得更低,并且EVM的测量结果开始下降。单独测试ADRF6801时,EVM将在大约−25 dBm时开始下降。但是,当ADRF6801驱动ADRF6510时,EVM直到−40 dBm才开始下降。在较低的信号水平下测量两个器件时,EVM会有所下降,这主要是由ADRF6510产生的噪声导致的。但是,浴盆图的噪底更为平坦且一致,并且由于基带可变增益,分辨较小信号的能力比ADRF6801驱动ADRF6510时要强很多。

有关ADRF6510和ADRF6801更详细的EVM测量可参考各自的数据手册。

测量结果:包含ADC的完整信号链

图7至图16中的信号链包括ADRF6801、ADRF6510和AD9248。全部三个器件相互之间均为直流耦合。ADRF6801和ADRF6510之间的共模电压为2.6 V。ADRF6510和AD9248之间的共模电压为2.0 V。ADC满量程电压为2 V。对ADRF6801的输入功率进行扫描,同时改变ADRF6510的增益,以便将ADC输入设为−3 dBFS的适当信号电平。使用ADC和Visual Analog软件测量SNR、SFDR、THD、HD2和HD3。使用Agilent 8665B低相位噪声信号发生器,将采样速率设为65 MSPS。使用两种不同的ADRF6510滤波器带宽:5 MHz和30 MHz。此外,将ADRF6510的前置放大器增益从6 dB改为12 dB。输入ADRF6801的RF信号为895 MHz,LO信号设为900 MHz,从而产生5 MHz中频信号音。使用100 MHz作为参考。对参考信号进行4分频,产生25 MHz PFD频率。采用型号为119-3651-00的Wenzel晶振产生100 MHz信号。

本电路笔记收集的数据显示AD9248ADC的SNR (71.6 dB)和SFDR (80.5 dBc)性能超过了ADRF6801和ADRF6510组合的性能。系统的总SNR和SFDR主要受限于ADRF6510的输出噪声,增益为20 dB时其额定值为−130 dBV/√Hz,滤波器带宽为30 MHz,在中间频带测量。(有关ADRF6510噪声与增益和带宽设置的更多信息,请参考ADRF6510数据手册)。

ADRF6510滤波器在高输入功率水平时表现出压缩特性(本例中为低增益),增加了谐波失真。基本上,在低输入功率水平下,ADC测量ADRF6510的输出噪底,并且HD2和HD3信号音低于此噪底。由于在较低的输入功率下具有较高的增益,ADRF6510的输出噪底有所增加。

图7和图8显示整个信号链(包括ADC)的SNR。在低功率水平下,SNR几乎逐dB下降。ADRF6510的增益为最大值,并且无法继续在较低的输入功率水平下提供−3 dBFS。信号幅度下降,而噪声相对保持恒定;因此,SNR下降。当信号和增益足以达到−3 dBFS时,SNR达到恒定水平。使用抗混叠滤波器3可获得最佳SNR,虽然分散在所有滤波器之间的只有大约1 dB,但抗混叠滤波器1除外,相比其余滤波器,该滤波器使SNR变差。

当ADRF6510滤波器设为30 MHz时,在最高的输入功率下SNR大幅下降,如图8所示。这是因为ADRF6510滤波器的压缩导致HD2和HD3突然下降,而整个噪底急剧增加。

图9和图10显示使用不同抗混叠滤波器时,整个系统的SFDR。滤波器4和滤波器5表现很差,在大部分输入功率范围内的SFDR为40 dB。这是因为HD3信号音限制了SFDR。对于其他抗混叠滤波器,在大部分范围内SFDR都超过了60 dB。由于主信号音并非−3 dBFS,输入功率较低时SFDR略微下降。

在较高的输入功率水平下,SFDR受限于ADRF6510滤波器压缩产生的谐波。

图11、图12、图13和图14显示系统的HD2和HD3。抗混叠滤波器4和5再次表现出了较差的性能,HD2性能约为−55 dBc,而HD3仅为−40 dBc。滤波器1、2和3的表现要好得多,HD2和HD3优于−70 dBc。

在输入功率范围内的低端,HD2和HD3分量比噪底还小,实际记录下来的是噪声。ADRF6510的增益降至足够低以后,输出噪声下降,显示出HD信号音,从而可进行适当测量。

在输入功率范围内的高端,HD2和HD3大幅下降。这是ADRF6510滤波器的压缩导致的。

测试并显示了5个抗混叠滤波器。相比LC和RLC类滤波器,RC类滤波器具有好得多的谐波失真性能。使用ADRF6510驱动AD9248时,建议采用转折频率尽可能低的RC滤波器,以便应用的所有指标都达到最佳值。

共模扫描

在ADRF6510的输出和AD9248的输入之间采用非2 V的共模电压,同时保持良好的性能是可能的。

图15和图16显示共模扫描的全部标准指标。共模电压范围为1.5 V至3 V时,系统具有良好的性能。低共模电压下的性能下降主要是由ADRF6510导致的,而高共模电压下的性能下降由ADRF6510和AD9248的组合所导致。对于ADRF6510/AD9248而言,将共模电压设为2.25 V可获得最佳性能。

常见变化

不同的IQ解调器、PLL和VCO、ADC

ADI公司提供其他类型的集成式IQ解调器,如ADRF6806 和ADRF6807。这些IQ解调器的射频频率范围分别为50 MHz至525 MHz和700 MHz至1050 MHz。两款器件的输出共模电压均为1.65 V,与3.3 V驱动器和ADC具有更佳的兼容性。

ADI公司还提供可将IQ解调器功能与频率合成器功能相分离的解决方案。工作频率范围相同的IQ解调器有:ADL5380和ADL5382和 ADL5387。这些IQ解调器的不同之处包括动态范围和正交系统。

集成VCO的频率合成器产品有:ADF4350、 ADF4351和 ADF4360,可在135 MHz至4350 MHz的宽频率范围内工作,具有不同相位噪声和输出功率指标。

在正交解调器之前加入一个诸如ADL5330的级联低噪声可变增益放大器(VGA)不仅可为系统带来更多增益,还有助于改善总系统噪声性能(假设VGA噪声系数低于正交解调器)。后续级的噪声系数通过初始VGA的增益进行分频处理。加入一个VGA而非固定增益放大器的另一个好处是可以设计AGC环路,从而将正交解调器的输入信号保持在固定电平。为了最大程度减少失真,这一限制施加于正交解调器和任何后续级信号电平的能力非常重要。

电路评估与测试

信号发生器包括

- Agilent E4438C矢量信号发生器

- Agilent 8665B信号发生器

- 型号为119-3651-00的Wenzel晶振(100 MHz)

基带信号捕获器件有:

- Agilent DSO90604A示波器

EVM运算器件包括:

- Agilent 89600 VSA软件

- 运行Windows XP的PC,通过USB电缆连接到Agilent DSP90604A示波器

电源包括

- ±5 V电源除AD8130电路板需要±5 V外,所有电路板均需要+5 VAgilent E4438C矢量信号发生器

评估板包括

- ADRF6801-EVALZ (需要一个)

- ADRF6510-EVALZ(需要一个)

- AD9248-BCP-65EBZ(需要一个)

- HSC-ADC-EVALB-DCZ(需要一个)

- AD8130-EBZ (如果进行EVM测量则需要两个)

开始使用

如需使用ADRF6801、ADRF6510、AD9248和数据捕捉卡HSC-ADC-EVALB-DCZ,则需使用评估软件控制每个器件的不同部分。此软件可在工具、软件和仿真模型链接中的各个产品网页上找到。下载和安装软件后,将USB电缆从电脑连接到评估板,然后针对需要控制的器件运行软件。

图17显示了用于测试接收链的测试设置功能框图。注意,信号路径从ADRF6801的输出端至AD9248的输入端,是完全差分的。

接收机测试设置的第一步是开启所有测试设备。测试设备预热时,电路板必须正确配置以便在信号链内正常使用。

在ADRF6801板上,旁路输出巴伦,以便在ADRF6801和ADRF6510之间获得完全差分的直流耦合信号路径。

在ADRF6510板上,执行下列操作:

- 旁路输入和输出巴伦

- 用1 μF电容取代普通COFS电容

在AD9248板上,移除巴伦,并将半刚性电缆按照巴伦尺寸进行焊接。这样可在ADRF6510和AD9248之间提供差分直流耦合连接。标准AD9248评估板提供单端交流耦合连接(通过巴伦)或单端直流耦合连接(通过板载AD8138放大器)。用户可使用单端设置,同时依然执行前文所述之全部测量(共模测量除外)。满量程电压设为2 V。在AD9248评估板上构建抗混叠滤波器。有多个表贴器件焊盘可用来构建抗混叠滤波器。

收集评估板,并将所有信号路径连在一起,如图17所示。将所有电路板连接至+5 V,然后插入AD9248板和数据采集板,并连接提供的电源。请确保电源电流与期望值一致。

图17. 测试直接变频接收机的功能框图

- 将矢量信号发生器的单端、50 ¬输出连接到ADRF6801评估板的RFIN。

- 将USB电缆从PC连接到示波器。

- 将ADRF6801的REFIN端口连接到低相位噪声源;此时Wenzel振荡器频率为100 MHz。

在Agilent E4438C矢量信号发生器上,执行下列操作:

- 将RF载波频率设置为895 MHz。

- 将幅度设置为−30 dBm。

- 接通RF端口。

在PC上启动Visual Analog软件。在软件中执行下列操作:

- 查找AD9248,打开FFT平均画布。

- 设置均值为20,然后设置“移动平均”。

- 运行软件,开始采集ADC数据。

从−50 dBm扫描至+4 dBm,以便在此测试设置下测试接收机。ADRF6510上的增益始终设置为实现−3 dBFS的ADC输入端信号电平,即1.0 V p-p差分信号。某些情况下,对于极小的信号电平,ADRF6510无足够的增益来达到1.0 V p-p差分电平。