LTC3225 5V 超级电容充电器后备电源

详情介绍

电路功能与优势

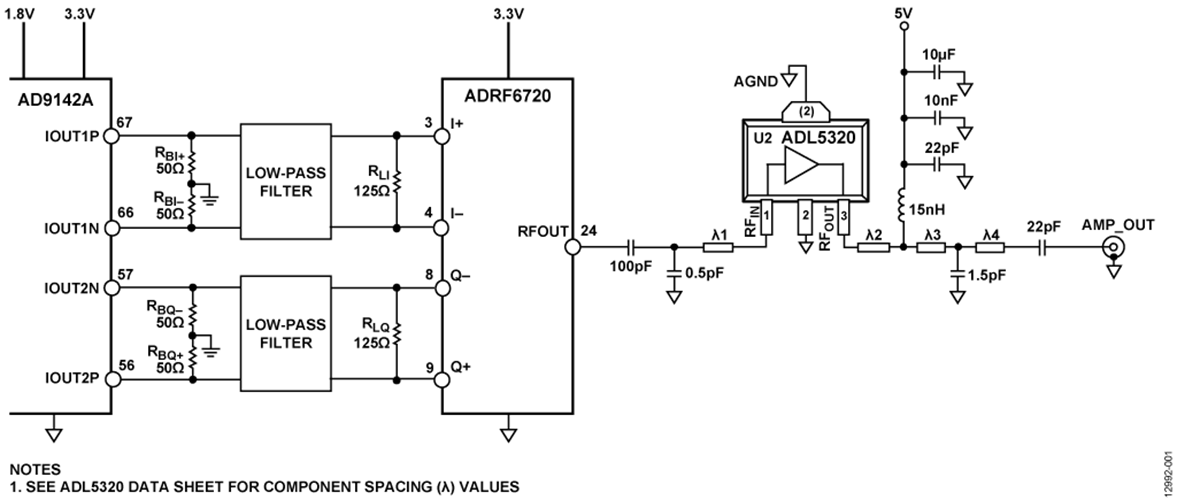

图1中的电路是一个宽带低失真RF发射器,集成双通道高速TxDAC+数模转换器(DAC)、宽带I/Q调制器和输出驱动器放大器。

器件匹配良好,且DAC与调制器、调制器与驱动器放大器之间直接接口,可为包括3G、4G和LTE在内的很多RF通信应用提供紧凑型解决方案。

器件匹配良好,且DAC与调制器、调制器与驱动器放大器之间直接接口,可为包括3G、4G和LTE在内的很多RF通信应用提供紧凑型解决方案。

电路描述

图1和图2中的RF发射器采用 AD9142A TxDAC、集成 ADRF6720 锁相环(PLL)/压控振荡器(VCO)的宽带I/Q调制器以及 ADL5320 ¼ W驱动器放大器。

DAC至调制器接口电路中的信号偏置和调整分别由四个以地为基准的电阻(RBI+、RBI−、RBQ+、RBQ−)和两个分流电阻(RLI、RLQ)控制。ADL5320驱动器放大器的输入和输出匹配由输入和输出端的分流电容实现。所需的匹配元件和位置参见ADL5320数据手册。

图1. 集成DAC和驱动器放大器的I/Q调制器简化电路图(未显示所有连接和去耦)

图2. 修改AD9142A评估板和ADRF6720评估板以便实现该电路

AD9142A满量程输出电流标称值和默认值均为20 mA。采用四个以地为基准的50 Ω电阻时(RBI+ = RBI− = RBQ+ = RBQ−),该电流产生500 mV直流偏置电平,并在每个DAC输出对上产生2 V p-p差分满量程输出电压摆幅。 2 V p-p电压摆幅可通过RL分流电阻(RL = RLI = RLQ)进行调节,该电阻与ADRF6720调制器的500 Ω I/Q输入阻抗并联。 500 mV直流偏置电平不受此调节的影响。 例如,若负载有效值为100 Ω差分,则每个单端输出将在250 mV至750 mV范围内摆动,但依然可以保持500 mV平均值 。

图3显示了所产生的p-p差分摆幅与RL限摆电阻和500 Ω并联差分输入阻抗的函数关系。

图3. 使用50 Ω偏置设置电阻时,有效交流限幅电阻与峰峰值电压摆幅之间的关系

I/Q滤波

DAC与调制器之间有必要放置一个抗混叠滤波器,以滤除奈奎斯特镜像、共模噪声和宽带DAC噪声。 应将该滤波器放置在直流偏置设置电阻与交流限幅电阻之间,

直流偏置设置电阻设置滤波器源阻抗,交流限摆电阻与ADRF6720 500 Ω输入阻抗的并联组合设置滤波器负载阻抗。

图4. 推荐的DAC调制器接口拓扑(fC = 300 MHz,五阶巴特沃兹滤波器)

System Level Simulation

图5显示了2140 MHz条件下I/Q调制器与驱动器放大器的仿真级联性能。AD9142A、ADRF6720和ADL5320的动态范围和增益匹配良好。 图5显示了39.4 dBm复合输出三阶交调截点(OIP3)以及−76 dBc左右的邻道泄露比(ACLR)性能。此仿真利用 ADIsimRF Design Tool来完成。

ADRF6720的线性度可通过MOD_RSEL(寄存器0x31,位[12:6])和MOD_CSEL(寄存器0x31,位[5:0])设置进行优化。 这些设置控制基带输入级的反相失真量,可校正失真。

图6到图11显示调节ADRF6720的MOD_RSEL寄存器和MOD_CSEL寄存器后,测得的输出二阶交调截点(OIP2)和OIP3曲线(在零中频、100 MHz和200 MHz复数中频优化)。

图6、图7和图8显示MOD_RSEL轴上每32步的优化OIP3性能;OIP3性能在零中频处与MOD_CSEL没有明显的函数关系。 但是,在较高中频频率下,MOD_CSEL的灵敏度更高。

通过优化MOD_RSEL和MOD_CSEL,OIP3在零中频约为42 dBm,在100 MHz中频约为45 dBm,在200 MHz中频约为48 dBm。

RSEL和CSEL调节不会对OIP2性能产生大幅影响;但是,在高中频频率处会有一些性能下降。

图5. ADIsimRF设计工具屏幕截图,显示AD9142A、ADRF6720和ADL5320的级联性能

图6. OIP3与MOD_CSEL和MOD_RSEL的关系(fRF = 2140 MHz,零中频,ADL5320输出功率为11 dBm)

图7. OIP3与MOD_CSEL和MOD_RSEL的关系(fRF = 2140 MHz,100 MHz中频,2340 MHz LO,ADL5320输出功率为11 dBm)

图8. OIP3与MOD_CSEL和MOD_RSEL的关系(fRF = 2140 MHz,200 MHz中频,2340 MHz LO,ADL5320输出功率为11 dBm)

图9. OIP2与MOD_CSEL和MOD_RSEL的关系(fRF = 2140 MHz,零中频,ADL5320输出功率为11 dBm)

图10. OIP2与MOD_CSEL和MOD_RSEL的关系(fRF = 2140 MHz,100 MHz中频,2340 MHz LO,ADL5320输出功率为11 dBm)

图11. OIP2与MOD_CSEL和MOD_RSEL的关系(fRF = 2140 MHz,200 MHz中频,2340 MHz LO,ADL5320输出功率为11 dBm)

选择输出功率水平

虽然该电路的输出功率电平可高达12 dBm,但在此电平下工作是不实际的,尤其是调制载波具有较高的峰均比时尤为如此。 为了获得可以接受的失真水平,需要进行大幅倒退。 邻道功率比(ACPR)已成为评估系统级失真的主流指标。

图12和图13显示ADL5320输出端测得的ACPR与输出功率的关系;它们分别为采用单载波WCDMA(测试模型1-64)和LTE(测试模型1_1 64QAM)时的三个中频情况。 系统在−2 dBm至+6 dBm输出功率范围内可实现约−75 dB至−80 dB的ACPR。 在采用LTE信号的情况下,ACPR定义为载波(带宽为4.515 MHz)中的功率与邻道(通道间隔为5 MHz)中的功率之比,同样也是在4.515 MHz带宽条件下测量。

图12. ADL5320放大器输出端ACLR与输出功率的关系(零中频,在2140 MHz优化ADRF6720上的RSEL和CSEL,1C WCDMA TM1-64)

图13. ADL5320放大器输出端ACLR与输出功率的关系(优化ADRF6720上的RSEL和CSEL OIP3,1C LTE TM1_1 64QAM)

OIP2和OIP3可通过调节上文中提到的MOD_RSEL和MOD_CSEL而得到改进;相应的,ACPR的改进见图13和图14。 在较高的输出功率电平下,这种改进更为明显。

图14. ADL5320放大器输出端ACLR与输出功率的关系(零中频,在2140 MHz优化与未优化ADRF6720上的RSEL和CSEL,1C WCDMA TM1-64)

图15. ADL5320放大器输出端ACLR与输出功率的关系(零中频,在2140 MHz优化与未优化ADRF6720上的RSEL和CSEL,1C LTE TM1_1 64QAM)

单个WCDMA和LTE在2140 MHz的频谱曲线分别如图16和图17所示。

图16. ADL5320放大器输出端的邻道功率性能(零中频,在2140 MHz优化ADRF6720上的RSEL和CSEL,1C WCDMA TM1-64)

图17. ADL5320放大器输出端的邻道功率性能(零中频,在2140 MHz优化ADRF6720上的RSEL和CSEL,1C LTE TM1_1 64QAM)

PCB布局建议

应特别注意DAC/调制器/放大器接口的布局布线。 PCB布局布线建议如下:

使所有I/Q差分走线长度保持良好的匹配。

滤波器端接电阻尽可能靠近调制器输入端放置。

DAC输出50 Ω电阻尽可能靠近DAC放置。

加宽经过滤波器网络的走线以降低信号损耗。

在所有DAC输出走线、滤波器网络、调制器输出走线、LO输入走线、放大器输入走线和放大器输出走线周围设置过孔。

将LO和调制器输出走线布设在不同的层上或彼此成90°角,防止耦合。

常见变化

本电路笔记所述的DAC和调制器接口可以用在任何设置为20 mA满量程电流的TxDAC数模转换器与需要0.5 V基带直流偏置电平的I/Q调制器之间。 TxDAC示例有:

AD9779A,

AD9788,

AD9125,

AD9144, 和

AD9148。I/Q调制器有:

ADL5370/

ADL5371/

ADL5372/

ADL5373/

ADL5374/

ADL5385/

ADL5386, 以及集成PLL/VCO的

ADRF6701/

ADRF6702/

ADRF6703/

ADRF6704 系列。

针对较高功率下的工作,推荐ADL5324 ½ W驱动器放大器。 ADL5320 和 ADL5324 必须调谐至各自的工作频率范围内。 这两款器件的数据手册都包含一些表格,其中提供了针对常用工作频率进行元件调谐的推荐值。

针对较高功率下的工作,推荐ADL5324 ½ W驱动器放大器。 ADL5320 和 ADL5324 必须调谐至各自的工作频率范围内。 这两款器件的数据手册都包含一些表格,其中提供了针对常用工作频率进行元件调谐的推荐值。

电路评估与测试

设备要求

需要以下设备。 可以用同等设备代替。

需要以下设备。 可以用同等设备代替。

- AD9142A 评估板(AD9142-M5375-EBZ),加入SMA连接器以便直接连接TxDAC电流输出

- ADRF6720 评估板(ADRF6720-EVALZ)

- ADI公司数字模式发生器(DPG)

- 用作时钟的信号发生器(R&S SMIQ 03B)

- 用作ADRF6720基准输入的信号发生器(R&S SMIQ 03B)

- 频谱分析仪(Agilent E4440A)

- 电源(Agilent E3631A,需要两个)

按照图18所示连接设置和测量系统。

将电源设为5 V,用于AD9142A评估板。

将电源设为3.3 V,用于ADRF6720评估板。

将电源设为5 V,用于ADRF6720评估板上的ADL5320。

将用作时钟的信号发生器设为1.5 GHz (5 dBm),将用作ADRF6720基准输入的信号发生器设为153.6 MHz (4 dBm)。

接通电源和信号发生器。 将频谱分析仪设为2140 MHz。

按照图19所示,通过USB并使用AD9142A SPI控制软件设置AD9142A,然后运行。 请参考AD9142A评估板快速入门指南。

按照图20所示设置DPG,然后运行。 请参考AD9142A评估板快速入门指南。

按照图21所示设置ADRF6720,然后运行。 请参考 ADRF6720-EVALZ User Guide ( UG-689)。

图18. 测试设置

图19. AD9142A SPI控制用户界面设置

图20. 使用DPG下载器软件设置DPG

图21. 使用ADRF6720控制软件设置ADRF6720