LT8641 2MHz、5V、3.5A 降压型转换器

详情介绍

概览

产品详情

DE0-Nano-SoC 开发套件提供了一款围绕 Altera 片上系统 (SoC) FPGA 构建的坚固型硬件设计平台,其把最新的双核 Cortex-A9 嵌入式内核与业界领先的可编程逻辑电路组合起来以实现终极设计灵活性。如今,用户能够利用与一个高性能、低功率处理器系统配对的巨大可重配置性的功能。Altera 的 SoC 集成了一个基于 ARM 的硬处理器系统 (HPS),该系统由处理器、外设以及使用一个高带宽互连主干网与 FPGA 内部结构实现无缝连接的存储器接口组成。DE0-Nano-SoC 开发板配备了高速 DDR3 存储器、模数转换能力、以太网联网、以及有望实现许多令人兴奋之应用的众多其他功能。

DE0-Nano-SoC 开发套件包含了把该开发板与一台运行 Microsoft Windows XP 或后续操作系统的计算机一起使用所需要的全部工具。

DE0-Nano-SoC 套件与 Atlas-SoC 套件的不同之处是什么?

对于 DE0-Nano-SoC 套件和 Atlas-SoC 套件来说硬件是相同的。唯一的不同是两款套件的启动开发工作流程。用户能够在 Atlas-SoC 套件上免费使用 DE0-Nano-SoC 套件资源,反之亦然。

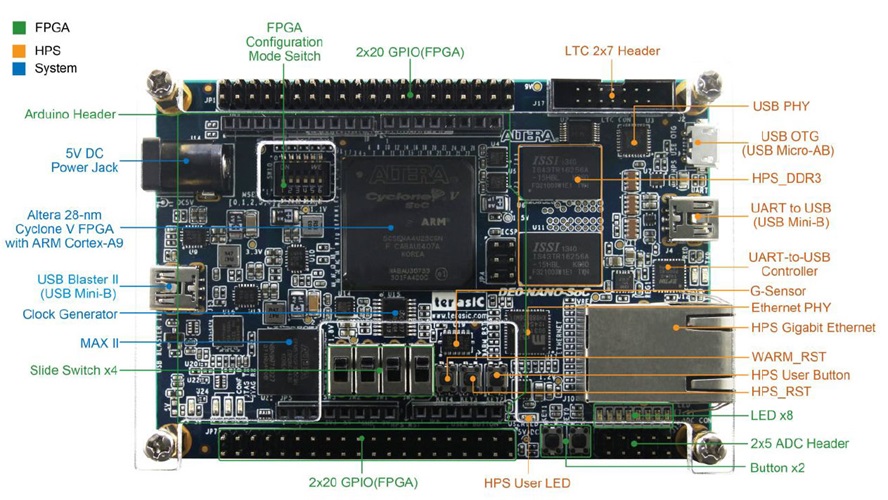

DE0 Nano SoC 开发平台 (顶视图)

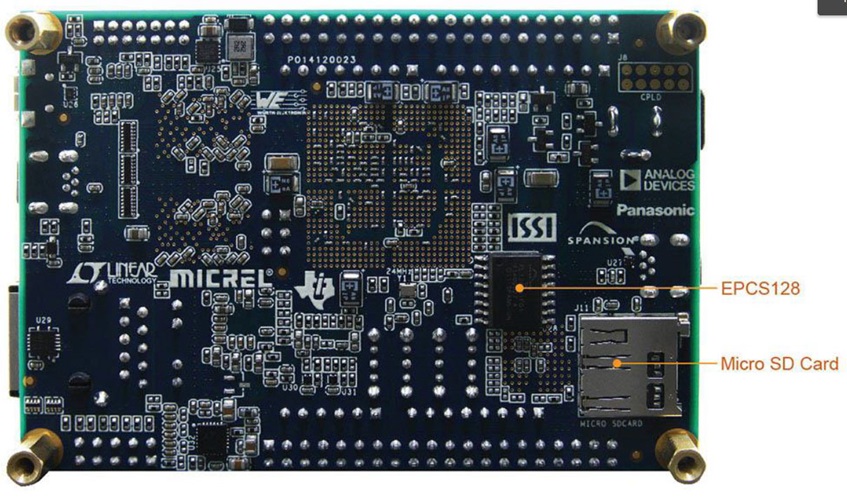

DE0 Nano SoC 开发平台 (底视图)

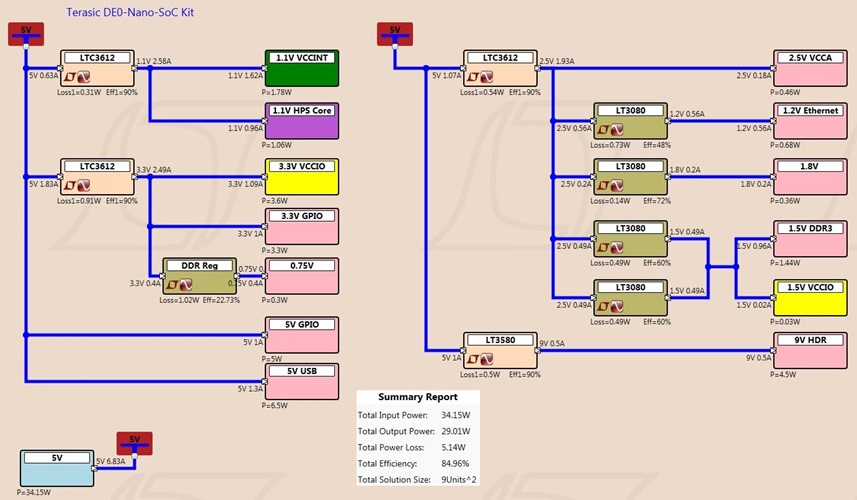

DE0 Nano SoC 电源树

| 功能 / 电源轨 | 器件型号 | 器件描述 |

| 1.1 V: VCCINT (FPGA 电源树) 1.1V: HPS Core (FPGA 硬化内核) 3.3V: VCCIO |

LTC3612 | 3A、4MHz 同步降压型 DC/DC 转换器 |

| 1.5V: VCCIO | LT3080 | 可调 1.1A、单电阻、低压差稳压器 |

| 9V: HDR | LT3580 | 具 2A 开关、软起动和同步功能的升压 / 负输出 DC/DC 转换器 |

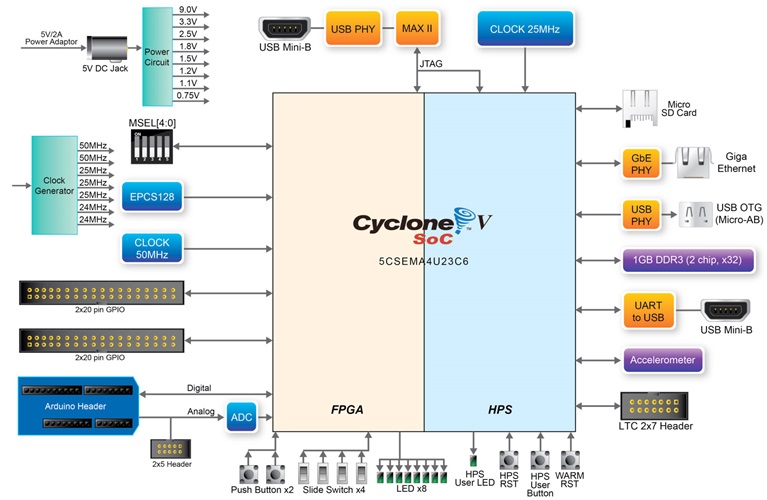

DE0 Nano SoC 方框图